RISC-VSoCFPGA架構為Linux帶來了實時性

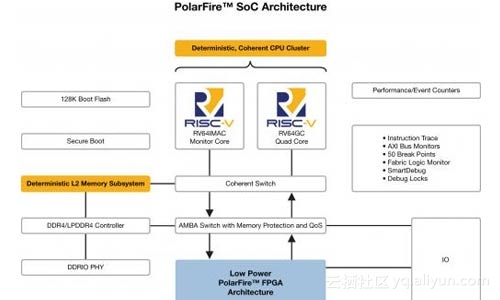

Microchip通過其Microsemi Corporation子公司宣佈推出新型SoC FPGA架構,擴充套件其Mi-V生態系統。新系列將功耗最低的中端PolarFire FPGA系列與基於開放式,免版稅的RISC-V指令集架構(ISA)的完整微處理器子系統相結合。

PolarFire SoC架構為多核連貫中央處理單元(CPU)叢集中的Linux平臺帶來了實時確定性和非對稱多處理(AMP)功能。與SiFive合作開發的PolarFire SoC架構具有靈活的2 MB L2記憶體子系統,可配置為快取、暫存器或直接訪問記憶體。這使得設計人員要在豐富的作業系統中同時實現確定性的實時嵌入式應用,以適應協作的網路物聯網系統中的各種熱量和空間受限應用。

在由5G,機器學習和物聯網(IoT)融合驅動的計算新時代,嵌入式開發人員需要豐富的基於Linux的作業系統。這些必須滿足更低功耗,熱約束設計環境中的確定性系統要求,同時滿足關鍵的安全性和可靠性要求。傳統的片上系統(SoC)現場可程式設計門陣列(FPGA)在單個晶片上將可重新配置的硬體與支援Linux的處理相結合,為開發人員提供了理想的定製裝置,但功耗過大,安全性和可靠性還有待驗證。除了Microchip的內建雙通道邏輯分析儀SmartDebug之外,PolarFire SoC還包括廣泛的除錯功能,包括指令跟蹤、50個斷點指令、可配置的被動執行時高階可擴充套件介面(AXI)匯流排監控程式和FPGA結構監控程式。

PolarFire SoC架構包括可靠性和安全性功能,如所有儲存器上的單錯誤糾正和雙錯誤檢測(SEC-DED),實體記憶體保護,差分功耗分析(DPA)安全加密核心,防禦級安全啟動和128Kb快閃記憶體啟動記憶體。使用PolarFire SoC的評估和設計得到了antmicro Renode系統建模平臺的支援,該平臺現在與Microchip的SoftConsole整合設計環境(IDE)整合,用於針對PolarFire SoC的嵌入式設計。PolarFire SoC開發套件現已上市,包括支援PolarFire FPGA的HiFive Unleashed擴充套件板和帶有RISC-V微處理器子系統的SiFive HiFive Unleashed開發板。

相關文章

- 為無伺服器的Web應用程式帶來實時性 - ITNEXT伺服器Web

- 如何實現彈性架構架構

- 微服務架構帶來的分散式單體微服務架構分散式

- 當動態伸縮無法實現時,很多優秀架構就只剩下複雜性了架構

- 實時數倉:Kappa架構APP架構

- 幽默:沒有資料庫的架構來了資料庫架構

- 為 Luy 實現 React Fiber 架構React架構

- 如何為你的 Linux 終端帶來好運Linux

- 帶你瞭解極具彈性的Spark架構的原理Spark架構

- 1.2.1. 非多租戶架構帶來的挑戰架構

- 帶你動手實現 MVP+Clean架構!MVP架構

- 直播帶貨系統為商家帶來了怎樣的機遇?

- 再戰Transformer!原作者帶隊的Mamba 2來了,新架構訓練效率大幅提升ORM架構

- 讓資料為你帶來無限可能性

- TA來了!TA來了!TA帶著獎勵走來了!

- 核心業務“瘦身”進行時!手把手帶你搭建海量資料實時處理架構架構

- 數字化時代,DIY個性化消費將為企業帶來萬億市場

- 網際網路公司資料架構能為傳統行業帶來哪些啟示AU架構行業

- 網際網路公司資料架構能為傳統行業帶來哪些啟示XY架構行業

- 網際網路公司資料架構能為傳統行業帶來哪些啟示WX架構行業

- 短視訊同城拓客工具為商家帶來了什麼切實好處?

- 分散式架構篇 | 如何在分散式架構下完美實現“全域性資料一致性”?分散式架構

- 餓了麼分散式KV架構與實踐分散式架構

- 他來了! 他來了! 他帶著 Gopher 專屬衛衣來了~Go

- 精益生產諮詢為公司帶來了什麼?

- KubeVela + KEDA:為應用帶來“與生俱來”的彈性伸縮能力

- iOS架構:AOP實現區域性模組化iOS架構

- 阿里架構師耗時一個月整理的《java架構師學習路線》太全了阿里架構Java

- 【AAC 系列一】Android 應用架構新時代來臨!Android應用架構

- Linux 核心 101:NUMA架構Linux架構

- 華為資深架構師:Cloud Native架構一致性問題及解決方案架構Cloud

- 實時資料架構體系建設指南架構

- 為什麼 Lettuce 會帶來更長的故障時間?

- 為什麼前端工程越來越愛使用 Monorepo 架構?前端Mono架構

- 微軟將為Linux帶來巢狀式虛擬化支援微軟Linux巢狀

- Linux終端注意了!隱蔽性更強的後門木馬Rmgr來了Linux

- 帶有Apache Spark的Lambda架構ApacheSpark架構

- 我們來了!多雲架構時代,歡迎加入中國開源網路新勢力架構