編者按:UCLA以電路方向的研究和教學聞名於世界,Behzad Razavi教授和Asad Abidi教授更是世界聞名的電路大師。UCLA的研究生課程模擬積體電路設計(EE215A)正是由Razavi和Abidi兩位大師輪流授課。我們整理了其中精華部分與大家分享:)前情回顧:電路大師課系列-模擬積體電路設計第一講:緒論與線性時不變系統電路大師課系列-模擬積體電路設計第二講:傳輸函式,零極點的形成及時域響應電路大師課系列-模擬積體電路設計第三講:零極點與頻率響應電路大師課系列-模擬積體電路設計第四講:基本π網路(上)

同學們,助教哥雖然回國吃香喝辣,但是並沒有樂不思蜀,這次攜手UCLA研究生焦魔給大家帶來基本π網路(下)。

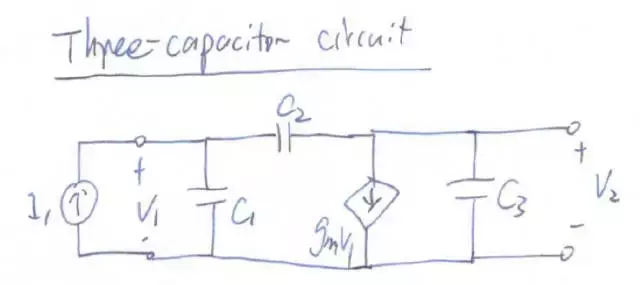

三電容電路

作為基本π網路的一種,三電容電路是理解類比電路頻響、放大器穩定性、開關-電容放大器、開關-電容積分器、取樣保持放大器的基礎。從多種不同的角度深刻理解三電容電路是類比電路設計入門的關鍵,同時三電容電路也是各大電路公司面試常用的題型。

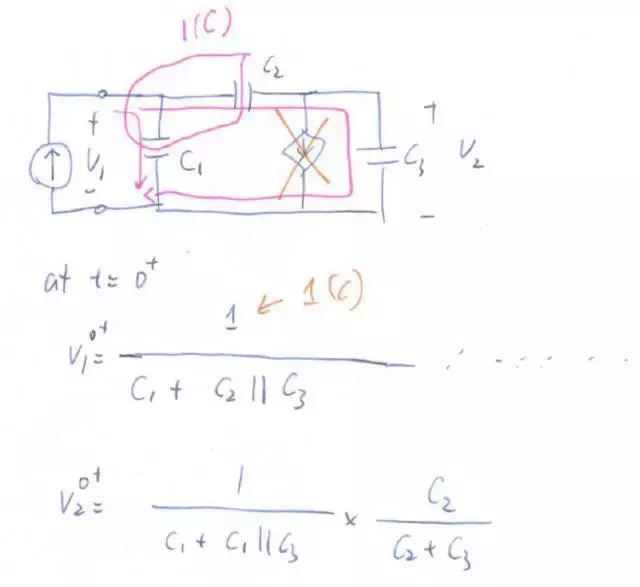

首先,這個電路有三個電容,但是三個電容形成一個環,電路只有兩個獨立的狀態變數(state variable),所以這個電路的傳輸函式只有兩個極點。

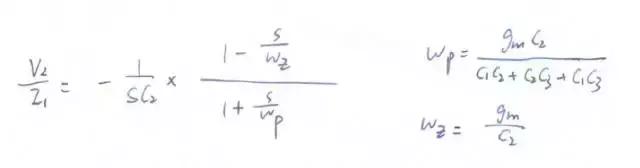

現在我們根據上一期講的基本π型函式列出傳輸函式V2/I1(不記得的同學可以去電路大師課系列-模擬積體電路設計第四講:基本π網路(上)回顧一下):

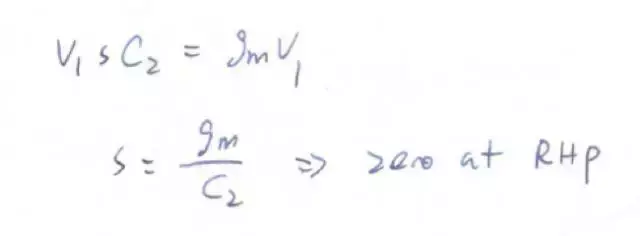

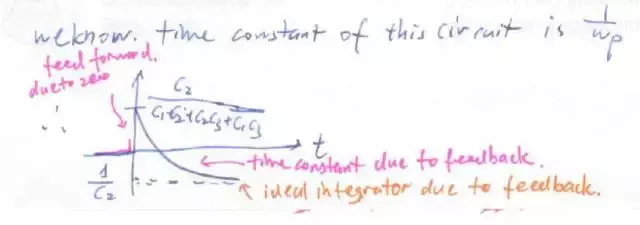

零極點的位置如下圖,有一個極點在原點,注意有一個零點在右半平面。

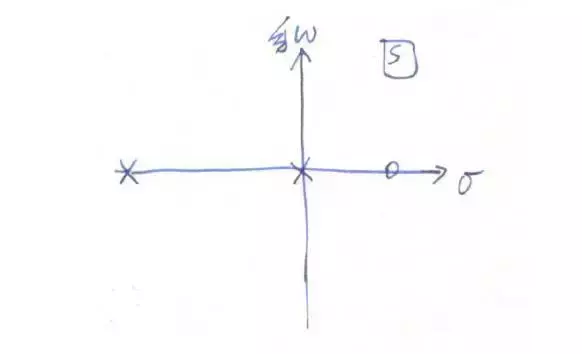

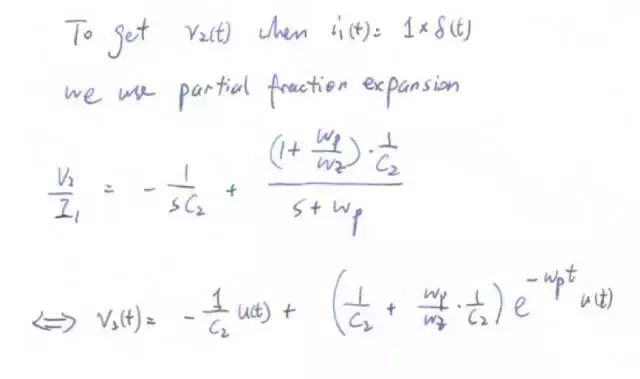

假設拉普拉斯域I1(s) 為 1,或者時域i1(t)為1*δ(t),我們可以透過拉普拉斯反變換找出v2(t):

我們發現,v2(t) 由一個階躍項和一個指數項組成,指數項會衰減到0,但是階躍項會一直保持。合在一起的總響應就是一開始有一個反向的過沖(overshoot),然後會以指數衰減的方式穩定到一個固定的終值。

現在我們換一種方式來分析零極點。之前我們講過,極點是由電路的純粹的拓撲結構所定的,每一個網路函式都有一樣的極點。

三電容電路零極點分析

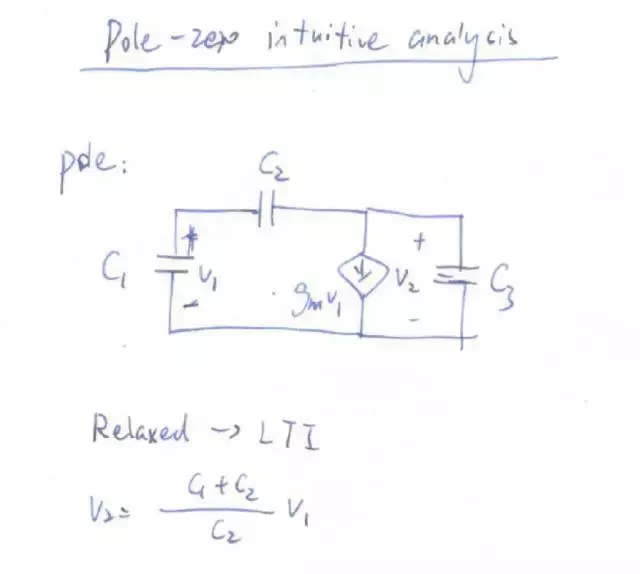

現在我們來看這個純粹的電路。假設這個電路是零狀態的(relaxed),那麼這個電路是線性時不變的(LTI),所以C1 C2組成了一個分壓器,那麼我們可以用V1來表示V2。

但是V2由是受控源兩端的電壓,而這個受控源也受到V1的控制,所以就變成了壓控電流源被自己兩端電壓所控制。一個被自己電壓控制的電流源就是一個電阻。所以我們可以算出該電阻:

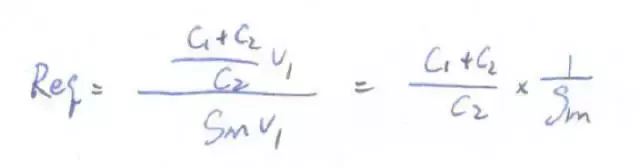

於是,三電容電路變成了下圖。這個電路的時間常量很好算了,算出來果然跟我們之前算的一個極點吻合。

另一個極點呢?

我們現在假設C2 C3上的t=0- 時的初始狀態為這樣:

當t=0時,我們發現整個電路沒有電流,C2 C3上的電壓一直保持著,這種能夠保持初始狀態的網路,一定有一個極點在原點。我們可以舉一個最簡單的例子,一個電容可以保持電壓,所以電容的阻抗這個網路函式有一個極點在原點。

這也與我們之前的推導吻合。

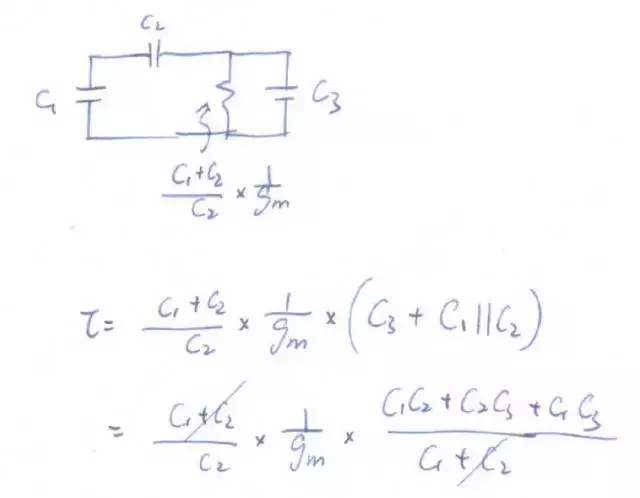

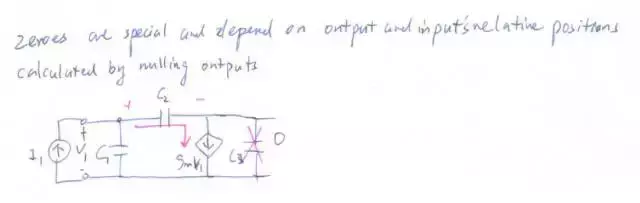

現在找零點,我們之前學過,零點是很特別的,是由激勵和響應的相對位置決定的。找零點需要抵消響應。現在我們把響應V2 抵消掉,如圖:

那麼C3沒有電流,受控源的電流等於C2的電流,但是C2的電流由可以被直接用V1表示出來,所以:

三電容電路時域分析

然後,我們從時域的角度把三電容電路的機理再過一次(非常重要!是深入理解三電容電路並幫你透過面試拿到offer的關鍵!)。

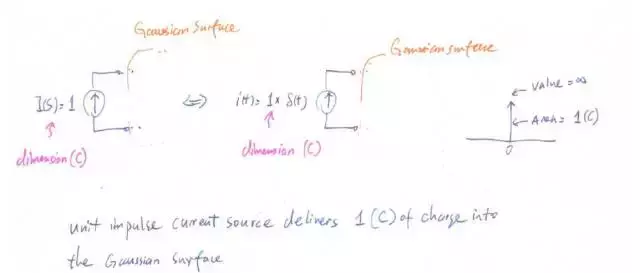

我們必須要先理解衝激電流的物理意義。單位衝激電流在拉普拉斯域的表示為1。注意這個1是有單位的,單位是庫倫,大家可以思考一下為什麼電流的拉普拉斯轉換的單位是庫倫。在時域裡,單位衝激函式前面的1的單位也是庫倫,因為單位衝激函式的積分為1,但是電流的積分必須是庫倫,所以這裡的1代表了一個包裹的1庫倫電荷,這個1庫倫的電荷只需要0時間就可以被輸送,因為在t=0的時候,電流無窮大。

所以,單位衝激電流的物理意義就是用0時間透過無窮大的電流向一個高斯面裡輸送了1庫倫電荷。

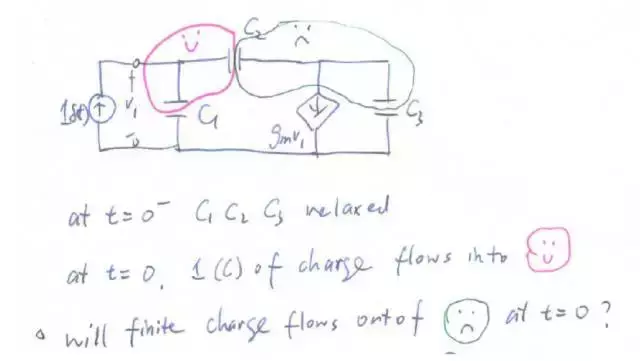

現在回到三電容電路,在t=0-時,三個電容都沒有初始電荷。在t=0時,1庫倫的電荷被注入到了紅色高斯面裡。現在的問題是,會不會有有限量的電荷在t=0時流入綠色高斯面。我們來分析這個情況:

如果有有限量的電荷流入綠色高斯面,那說明受控源gmv1必須是無窮大,因為無窮大的電流才能在0時間內輸送有限的電荷,有限的電流在0時間內輸送0電荷。

這表示v1是無窮大,但是v1無窮大的話,紅色高斯面內必須有無窮大的電荷,這不可能,因為衝激電流所攜帶的電荷是有限的。所以受控源電流是有限的,受控源在0時間內不輸送任何電荷。所以在t=0+時,只有電荷會在C1 C2 C3 中重新分佈,1庫倫的電荷會在C1+C2||C3這個總電容上建立一個電壓v1(0+)。C2 和C3必須形成一個分壓器,因為C2的右極板和C3的上極板的電荷總和為0。這樣我們可以推出v2(0+):

化簡v2(o+),我們可以得到:

這跟我們之前用拉普拉斯轉換得到的結果一致!

下面看最終狀態,當電路達到最終狀態時,所有的狀態變數都不再改變了(除非我們有共振或者不穩定的特殊情況,然而這個電路顯然沒有),這說明受控源gmv1必須為0,v1必須為0。但是當t>0時,紅色高斯面內的電荷就不再會改變了,因為獨立電流源為0,所以所有1庫倫的電荷都必須被“擠壓”到C2上,產生電壓1/C2。因為v1(∞)為0,所以我們可以算出v2(∞)為-1/C2。

這又跟我們用拉普拉斯轉換得到的結果一致!

我們之已經分析過,這個電路只有一個非無窮大的時間常量,所以這是一個“準一階電路”。對於這種電路,只要我們知道在t=0+的初始值和t=∞的終值,中間的行為就是一個一階指數衰減。所以我們得到與之前一致的響應:

引入非理想效應

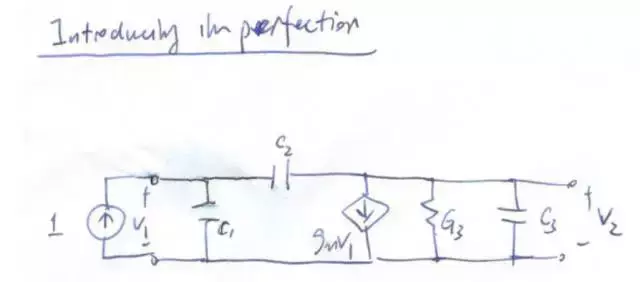

接著我們引入一個不理想效應,在受控源處並聯一個電導G3(有沒有覺得下面的電路圖很熟悉?對了,就是MOSFET小訊號電路基本就長這樣)。

重新使用基本π型函式列出傳輸函式:

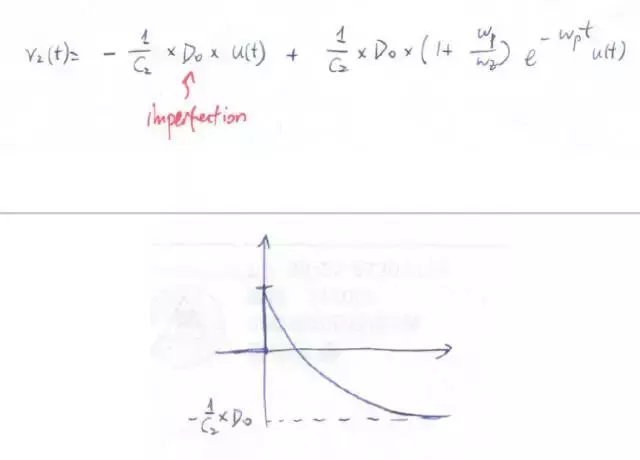

使用拉普拉斯反變換,我們得到

這裡,D0成為了誤差項,如果要讓D0非常接近於1,gmR3要遠大於1+C1/C2。

我們來從時域角度看這個問題:

如果G3不為0,那麼在終值狀態時,會有一個迴圈的電流流過G3。所以gmv1不為0,那麼v1不為0。這樣,並非所有的1庫倫電荷都被“擠壓”到了C2上,這就是導致誤差項的原因。對於類比電路而言,我們希望精確地放大訊號,放大倍數最好是元件之間的比例。假如我們的衝激電流源變成了vsC1δ(t),或者說C1 取樣了一個電壓源vs,C1在t=0時被放置到三電容電路里,如果G3為0,那麼響應v2終值將為準確的電容比例-C2/C1 vs。但如果G3不為0,這個比例就會有誤差。

三電容電路實際應用

看到這裡,大家一定會認為我們會拿MOSFET小訊號電路作為例子吧?非也,我們當然要找一個更有趣的例子。下面由焦魔為大家講一個三電容電路的例項:開關電容積分器(SCIntegrator)。

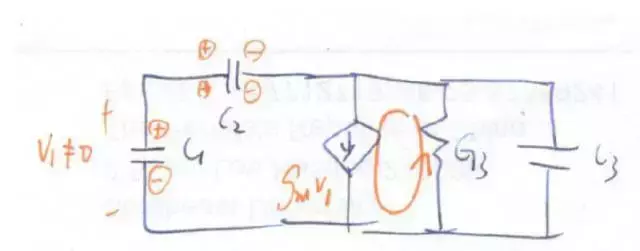

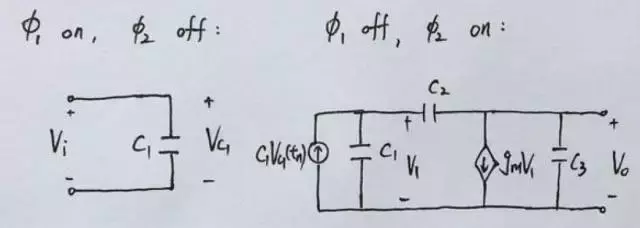

開關電容積分器是有源梯形濾波器(Active Ladder Filter)的基本組成模組。相比於使用電阻電容有源濾波器(OpAmp RC Filter),開關電容濾波器(SC Filter)具有精度高,噪聲小,受工藝、電壓、溫度影響小的優點(原因是我們不再需要電阻這個在晶片上很難做準的元件了)。下圖所示為一種基本的開關電容積分器(前向尤拉型,Forward Euler)的電路。

注:在該電路圖中,梯形符號代表跨導放大器(Operational Transconductance Amplifier, OTA)。跨導放大器和我們熟悉的運算放大器非常容易混淆,前者使用梯形符號,後者則是三角形符號。運算放大器的模型是一個壓控電壓源,跨導放大器的模型是一個壓控電流源。嚴格來講,我們通常所說的積體電路中的運算放大器實際上都是指跨導放大器;而我們做板級電路設計時使用的運放晶片才是真正的運算放大器。

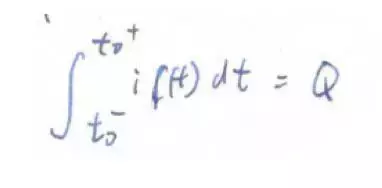

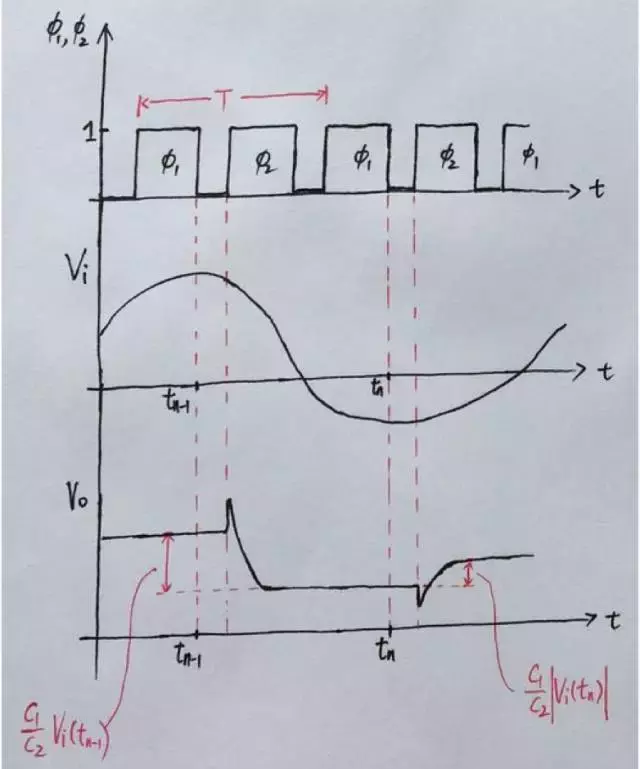

該電路有兩個工作相位。在φ1相位,電容C1的電壓跟隨輸入電壓vi變化,φ1相位結束時電容C1的電壓即為φ2相位開始時的初始電壓。φ2相位時電路的小訊號模型如下圖右側所示。其中衝激電流源等效代表了C1的初始電壓。電路的時序和波形圖如下:

電容C1在每個週期的取樣值在tk時刻確定,輸出電壓在每個週期φ2的開始時刻開始變化,先有一個瞬時的前向饋通,然後以指數衰減的形式穩定到最終的電壓值,理想情況下電壓的變化量由電容C1和C2的比值以及tk時刻取樣的輸入電壓值決定。同時,上一個週期存在C2上的電荷並沒有被釋放,所以這個電路就變成了一個積分器。如果考慮OTA有限的輸出電阻,這個電壓變化量會有一定的偏差。