I2S音訊匯流排學習(四)I2S介面設計

I2S音訊匯流排學習(四)I2S介面設計

一、資料傳送端的設計

圖1 傳送端

隨著WS訊號的改變,匯出一個WSP脈衝訊號,進入並行移位暫存器裝入DATA LEFT或DATA RIGHT,從而輸出資料被啟用。序列資料在時鐘下降沿移出。序列資料的預設輸入是0,因此所有位於最低位(LSB)後的資料將被設定為0。

二、資料接收端的設計

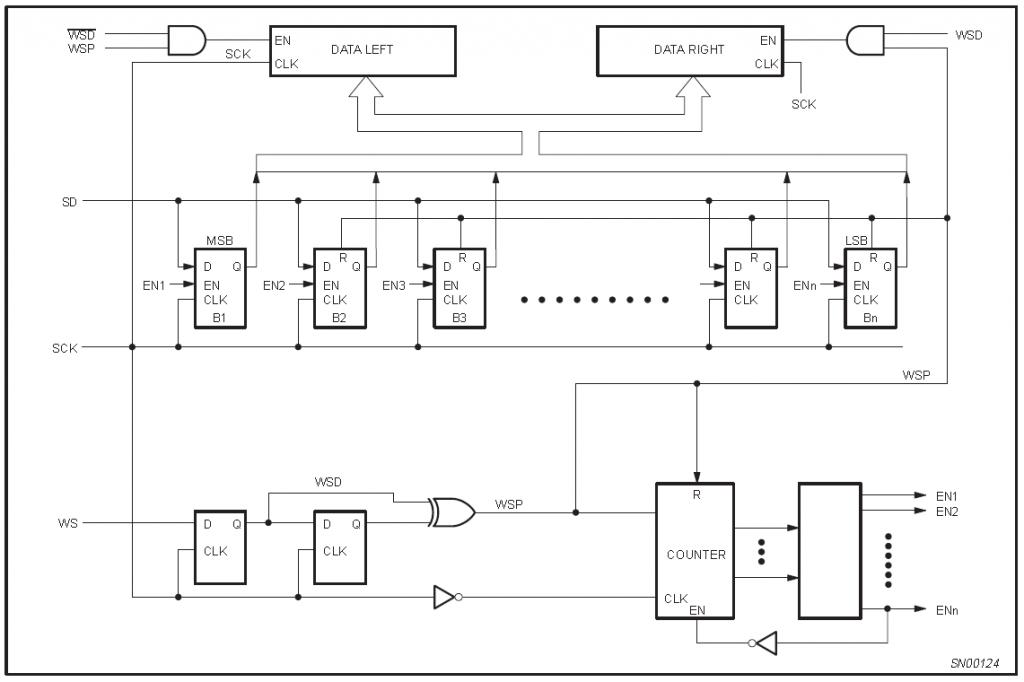

圖2 接收端

隨著第一個WS訊號的改變,WSP在SCK訊號的下降沿重設計數器。在“1 out of n”譯碼器對計數器數值進行譯碼後,第一個序列的資料(MSB)在SCK時鐘訊號的上升沿被存放進入B1,隨著計數器的增長,接下來的資料被依次存放進入B2到Bn中。在下一個WS訊號改變的時候,資料根據WSP脈衝的變化被存放進入左(聲道)鎖存器或者右(聲道)鎖存器,並且將B2一Bn的資料清除以及計數器重設,如果有冗餘的資料則最低位之後的資料將被忽略。注意:譯碼器和計數器(虛線內的部分)可以被一個n位元移位暫存器所代替,如圖3所示。

當計數計滿時,即ENn為高時,計算器EN訊號變成低電平,使計數器停止計數,同時也使串並轉換模組停止接收資料。

圖3 接收端

相關文章

- I2S音訊匯流排音訊

- 【音訊相關】I2S介面規範時序以及其同DSP的連線音訊

- i2s 協議協議

- CAN匯流排原理_學習

- 序列匯流排的學習

- [從原始碼學設計]螞蟻金服SOFARegistry之訊息匯流排原始碼

- CAN匯流排協議 學習筆記協議筆記

- 【ESP32】製作 Wi-fi 音響(HTTP + I2S 協議)HTTP協議

- 事件匯流排的設計與實現事件

- MACH SYSTEMS—匯流排介面轉換工具Mac

- 匯流排

- CAN(FD)、LIN匯流排通訊和資料庫設計工具-VDE資料庫

- 將Abp預設事件匯流排改造為分散式事件匯流排事件分散式

- 計算機組成原理之匯流排設計計算機

- 計算匯流排頻寬

- 004:ZYNQ_AXI匯流排學習筆記(1)筆記

- 手寫訊息匯流排LiveDataBusLiveData

- SpringCloud(六)Bus訊息匯流排SpringGCCloud

- [從原始碼學設計]螞蟻金服SOFARegistry之訊息匯流排非同步處理原始碼非同步

- 事件匯流排事件

- 前端匯流排前端

- AndroidEventBus (事件匯流排) 的設計與實現AndroidIDEdev事件

- RS-485匯流排通訊裝置

- 數倉實踐:匯流排矩陣架構設計矩陣架構

- 嵌入式作業6.3 CAN 匯流排程式設計程式設計

- 事件匯流排demo事件

- javascript事件匯流排JavaScript事件

- Spring Cloud Bus 訊息匯流排介紹SpringCloud

- WebWorker與WebSocket實現前端訊息匯流排Web前端

- ECU通訊:CAN匯流排模擬測試

- Kvaser—靈活多變的CAN匯流排介面方案

- 學習筆記-Verilog實現IIC匯流排協議筆記協議

- 使用SignalR為FineUI/Webform打造訊息匯流排SignalRUIWebORM

- I2C匯流排訊號時序分析

- 元件間通訊--利用mitt實現事件匯流排元件MIT事件

- Vue事件匯流排(EventBus)Vue事件

- Vue 事件中央匯流排Vue事件

- ARM 匯流排協議協議