Verilog程式碼風格

不管是什麼語言,如果大家都用同一套的程式碼風格,那麼交流起來就非常方便。除此之外,好的程式碼風格,還能讓你的工作變得輕鬆一些。(使用sublime的程式碼補全功能,就無需擔心這些複雜的變數名)。

如果你只使用Verilog,那麼建議用匈牙利命名法。如果是Verilog和VHDL混用,則建議用傳統命名法。因為VHDL不區分大小寫,用傳統命名法,有利於移植程式碼。

1、模組名跟檔名相同,都用小寫,頂層檔案要加上_top字尾。而testbench檔案則加上_tb字尾。

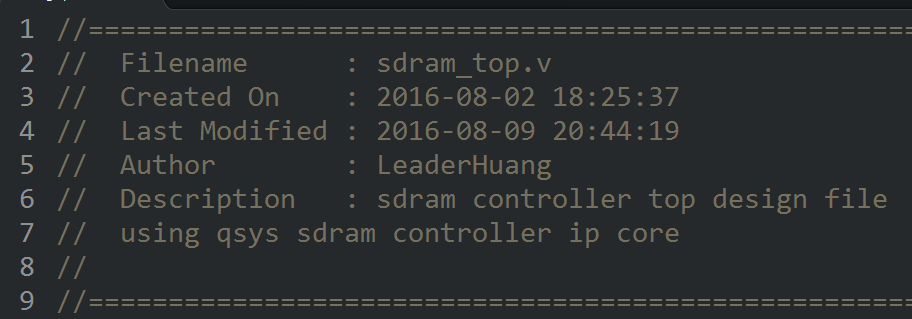

2、每個檔案的開頭,都要加註釋頭,並說明該檔案的作用。

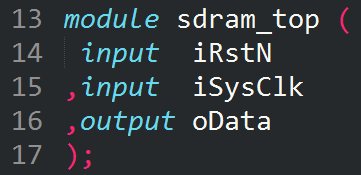

3、模組內部,除了第一行,其它行都以逗號開頭並對齊埠名,除錯時可以避免註釋某埠時帶來不必要的麻煩。

1位元的輸入埠以i開頭,1位元的輸出埠以o開頭,1位元的雙向埠以io開頭。

多位元的輸入埠以iv開頭,多位元的輸出埠以ov開頭,多位元的雙向埠以iov開頭。要跟鄰近的埠名對齊。(v是vector的意思)

4、1位元的reg型變數以r開頭,1位元wire變數以w開頭。

多位元的reg型變數以rv開頭,多位元的wire型變數以rw開頭。要跟鄰近的變數名對齊。

reg變數都要賦初值'b0,包括埠名(如 output reg oData='b0)。

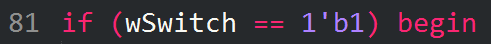

5、if、while語句中必須指明條件中的值,不允許寫成if(wSwitch)begin。

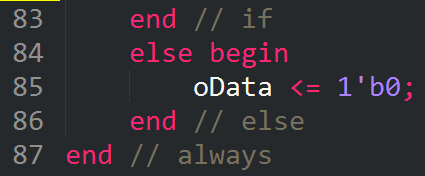

6、所有的end後面都要加上註釋,以標明是哪個關鍵詞的結束。

endcase和endmodule可以不加。

7、如果是低電平有效,就在變數名後面加上大寫N。

8、所有的begin和左括號(,都要跟對應的關鍵詞一行。(在同樣的面積下,能閱讀更多的程式碼)。

9、就算只有一行程式碼,都必須加上begin end。

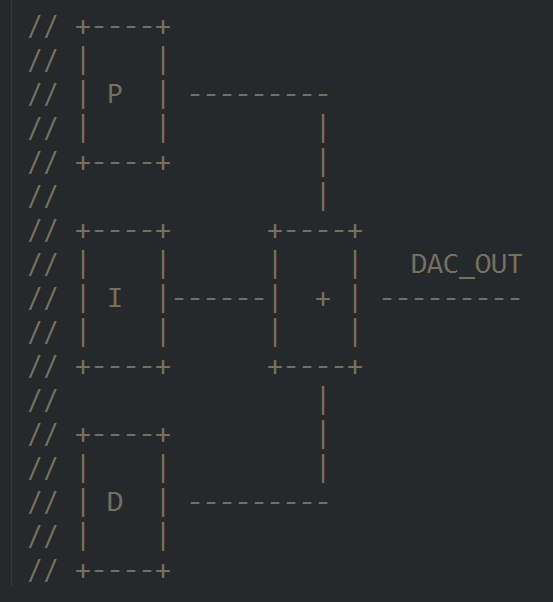

10、如果用到元件例化,要用AsciiArtStudio,畫好連線圖,轉成Ascii碼,放在對應的地方。

如果有狀態機,也要畫狀態轉換圖。

11、使用parameter或localparameter替代`define來定義常量,常量名全部都要大寫。

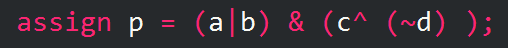

12、不依賴Verilog預設的優先順序,每個運算都加括號。

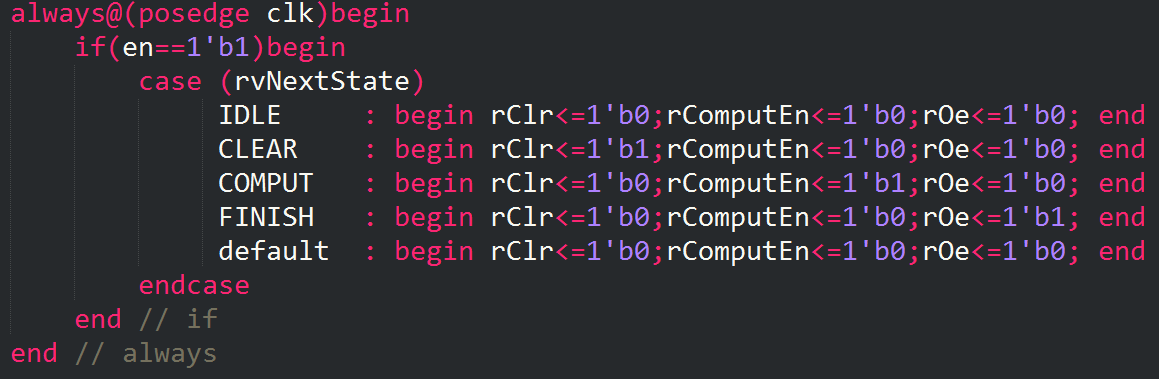

13、case語句下的分支要排列整齊。

14、always不要過於複雜,一個輸出就寫一個always,除非是關聯性很大的幾個輸出,可以寫在一起。

15、不使用隱式元件例化,在埠對映中,不加其它邏輯,如:AND、OR等。元件例化只完成接線的功能,加了其它邏輯,會影響分析程式碼。

16、做好縮排。

17、命名不使用拼音,要簡單易懂。

相關文章

- C 語言程式碼風格之 Linux 核心程式碼風格Linux

- JavaScript 程式碼風格指南JavaScript

- 程式碼的風格 (轉)

- Vue 前端程式碼風格指南Vue前端

- Google JavaScript 程式碼風格指南GoJavaScript

- FPGA可綜合風格程式碼FPGA

- 專案程式碼風格要求

- .editorconfig 程式碼風格配置

- Pycharm 程式碼註釋風格模板PyCharm

- 好的程式碼風格積累

- Typora 程式碼塊Mac風格化Mac

- 編碼規範(四)之程式碼風格

- Laravel 保持統一程式碼風格Laravel

- 前端程式碼規範 — JavaScript 風格指南前端JavaScript

- 不要再爭論程式碼風格了!

- 金庸筆下的良好程式碼風格

- Eclipse中使用google程式碼風格EclipseGo

- PEP 8 程式程式碼的編寫風格指南

- java程式設計規約----程式碼風格(一)Java程式設計

- PSR-1:基本的程式碼風格

- 部落格園使用sublime text風格的程式碼高亮樣式

- 如何選擇適合你的程式碼風格?

- 求求你規範下你的程式碼風格

- PHPStorm 程式碼格式化風格調整PHPORM

- 統一規範化程式碼的命名風格

- Go 語言程式碼風格規範-指南篇Go

- Go 語言程式碼風格規範-概述篇Go

- php-cs-fixer,自動修正程式碼風格PHP

- PHP PSR-2 程式碼風格規範PHP

- 《碼處高效:Java開發手冊》之程式碼風格Java

- JavaScript編碼風格指南JavaScript

- JavaScript 編碼風格指南JavaScript

- Javascript程式設計風格JavaScript程式設計

- Google C++程式設計風格指南(六):程式碼註釋GoC++程式設計

- 幽默:把Java寫成Python風格的程式碼JavaPython

- 談談JavaScript編碼風格JavaScript

- PHP編碼風格規範PHP

- 良好的HTML編碼風格HTML