一 為何要學習計算機基礎

python是程式語言,即python是語言

語言有英語、法語、葡萄牙語等,但凡是語言,都是用來溝通的介質。

程式設計師程式設計的本質就是讓計算機去工作,而程式語言就是程式設計師與計算機溝通的介質

程式設計師要想讓計算機工作,必須知道計算機能幹什麼,怎麼幹的,這也就是我們必須學習計算機基礎的原因

然而光有程式語言和硬體也並不能滿足大家的程式設計需求,為什麼這麼說呢?

程式用程式語言寫程式,最終開發出的結果就是一個軟體,既然是軟體,那就與騰訊qq、暴風影音、快播等軟體沒有區別了。這些軟體必須執行在作業系統之上,你肯定會問:為何要有作業系統呢?沒錯,遠古時代的程式設計師確實是在沒有作業系統的環境下,用程式語言之間操作硬體來程式設計的,你可能覺得這沒有問題,但其實問題是相當嚴重的,因為此時你必須掌握如何操作硬體的所有具體細節,比如如何具體操作硬碟(現在你得把硬碟拆開,然後你能看見的所有的東西,你都得研究明白,因為你程式設計時要用到它),這就嚴重影響了開發的效率,作業系統的出現就是執行於硬體之上,來控制硬體的,我們開發時,只需要呼叫作業系統為我們提供的簡單而優雅的介面就可以了

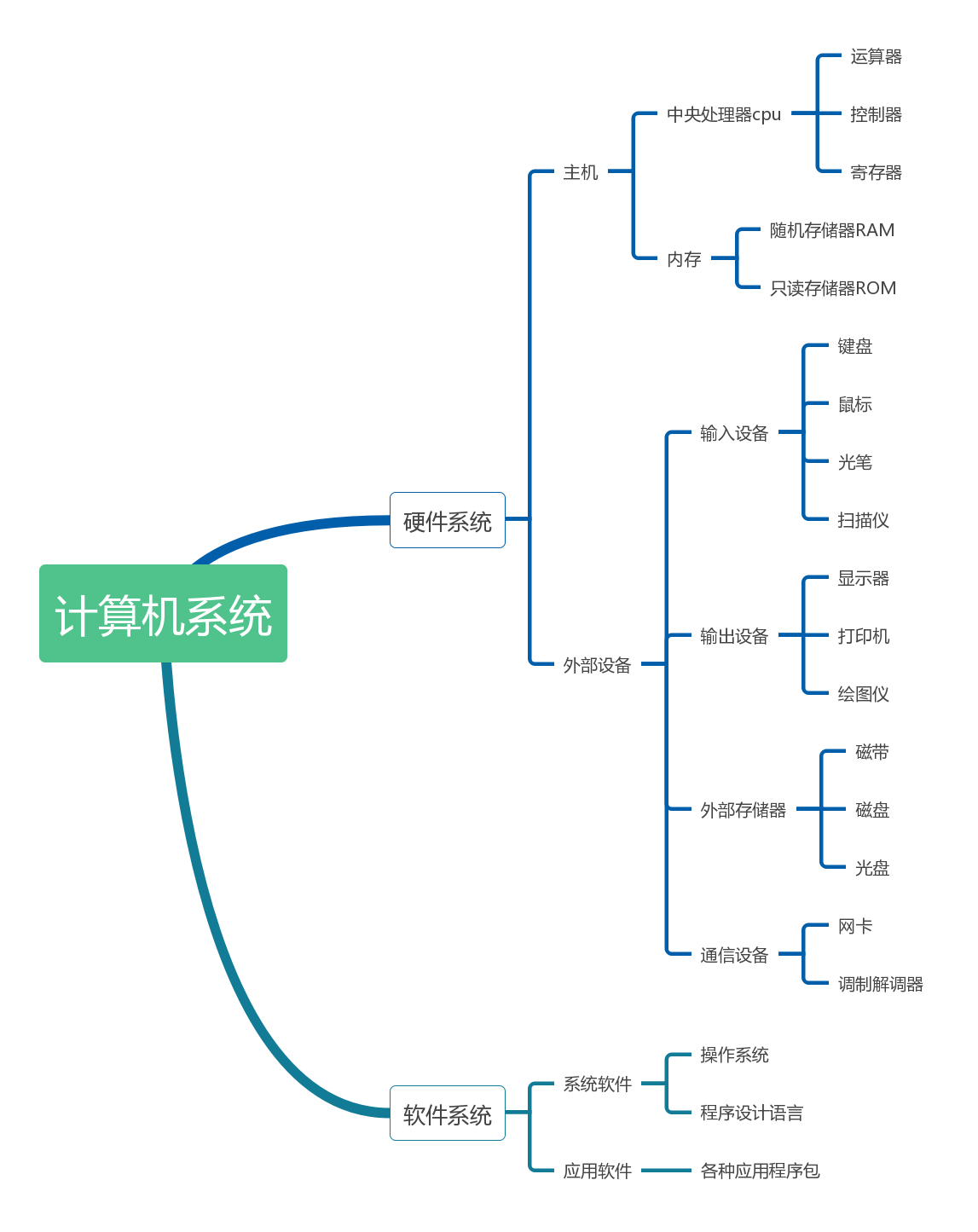

所以一套完整的計算機系統分為:計算機硬體,作業系統,應用軟體,如下圖。因而我們的python程式設計之路分為計算機硬體基礎,作業系統基礎,和python程式設計三部分,就讓我們先從計算機硬體學起吧

二 本節目標

- 瞭解計算機各元件及工作原理

- 瞭解計算機啟動流程

三 計算機硬體發展史

http://www.cnblogs.com/linhaifeng/p/6428430.html

四:計算機硬體介紹

計算機硬體有五大部分:(計算機是人的奴隸,可以將其當作一個人去看,請思考下述元件等同於人的哪些器官)

#1、控制器:計算機的指揮系統。控制器通過地址訪問儲存器,從儲存器中取出指令,經譯碼器分析後,根據指令分析結果產生相應的操作控制訊號作用於其他部件,使得各部件在控制器控制下有條不紊地協調工作。 #2、運算器:實現算術運算和邏輯運算的部件。 #3、儲存器:是計算機用來存放所有資料和程式的記憶部件。它的基本功能是按指定的地址存(寫)入或者取(讀)出資訊。 計算機中的儲存器可分成兩大類:一類是記憶體儲器,簡稱記憶體或主存;另一類是外儲存器(輔助儲存器),簡稱外存或輔存。 儲存器由若干個儲存單元組成,每個儲存單元都有一個地址,計算機通過地址對儲存單元進行讀寫。一個儲存器所包含的位元組數稱為儲存容量,單位有B、KB、MB、GB、TB等。 #4、輸入裝置:是向計算機中輸入資訊(程式、資料、聲音、文字、圖形、影象等)的裝置。常見的輸入裝置有:鍵盤、滑鼠、圖形掃描器、觸控式螢幕、條形碼輸入器、光筆等。 外儲存器也是一種輸入裝置。 #5、輸出裝置:主要有顯示器、印表機和繪圖儀等。外儲存器也當作一種輸出裝置。

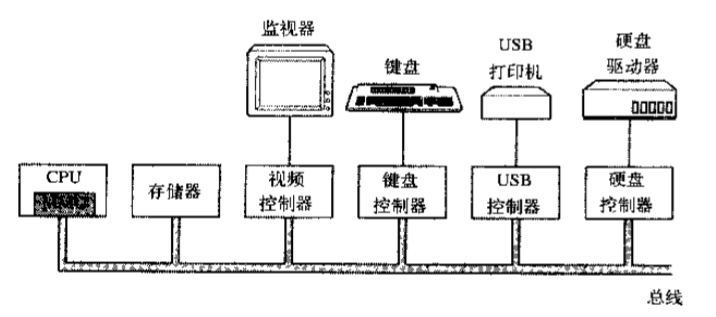

控制器+運算器=CPU,CPU、記憶體(主儲存器)以及其他I/O裝置都由一條系統匯流排(bus)連線起來並通過匯流排與其他裝置通訊

現代計算機的結構更復雜,包括多重匯流排,我們將在後面的小節介紹,此時暫且讓我們以下圖為例來介紹各個部件

cpu是人的大腦,負責控制全身和運算

記憶體是人的記憶,負責臨時儲存

硬碟是人的筆記本,負責永久儲存

輸入裝置是耳朵或眼睛或嘴巴,負責接收外部的資訊存入記憶體

輸出裝置是你的臉部(表情)或者屁股,負責經過處理後輸出的結果

以上所有的裝置都通過匯流排連線,匯流排相當於人的神經

上課開始,老師講課,學生聽課,老師是程式設計師,學生是計算機,學生的器官都是計算機各部分組成

1.你通過耳朵接收老師講的知識->輸入

2.通過自己的神經,將接收的資料存入自己的記憶體/短期記憶(匯流排、記憶體)

3.光聽不行,你還需要反應/處理老師講的知識,於是你的大腦/cpu從短期記憶裡取出知識/指令,分析知識/指令,然後學習知識/執行指令 (cpu取指、分析、執行)

4.你通過作業或者說話輸出你學到的結果

5.你想要永久將知識儲存下來,只能拿出一個筆記本,把剛剛學會的知識都寫到本子上,這個本子就是硬碟(磁碟)

4.1 處理器

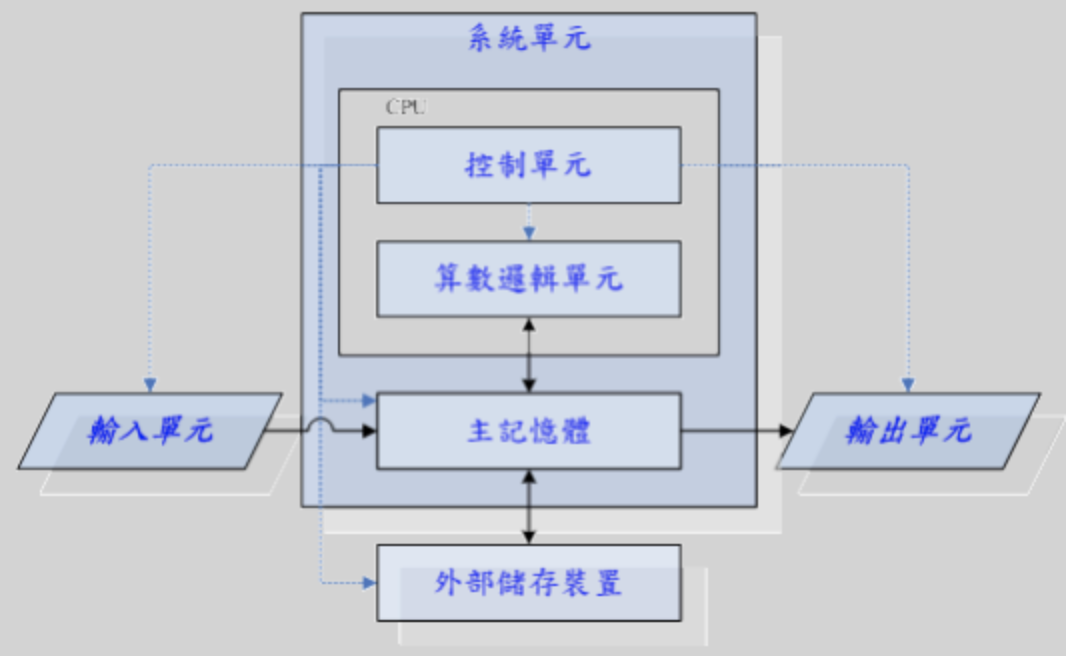

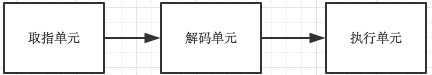

通常將運算器和控制器合稱為中央處理器(Central Processing Unit,CPU)。其中運算器用來主要負責程式運算與邏輯判斷,控制器則主要協調各元件和各單元的工作,所以CPU的工作主要在於管理和運算。可以說計算機的大腦就是CPU,它從記憶體中取指令->解碼->執行,然後再取指->解碼->執行下一條指令,周而復始,直至整個程式被執行完成。

既然CPU的重點在於進行運算和判斷,那麼要被運算與判斷的資料是從哪裡來的?CPU讀取的資料都是從主儲存器(記憶體)來的!主儲存器內的資料則是從輸入單元所傳輸進來!而CPU處理完畢的資料也必須先寫回主儲存器中,最後資料才從主儲存器傳輸到輸出單元。

綜合上面所說的,我們會知道其實計算機是由:輸入單元、輸出單元、CPU(控制單元、算術邏輯單元)與主儲存器五大單元構成的。也可以說CPU+輸入輸出+主儲存器構成了電子計算機的三大核心元件,相關性如下圖:

在超大規模積體電路構成的微型計算機中,往往將CPU製成一塊具有特定功能的晶片,稱為微處理器,晶片裡邊有編寫好的微指令集,我們在主機上的所有操作或者說任何軟體的執行最終都要轉化成cpu的指令去執行,如輸入輸出,閱讀,視訊,上網等這些都要參考CPU是否內建有相關微指令集才行。如果沒有那麼CPU無法處理這些操作。不同的CPU指令集不同對應的功能也不同,這就好比不同的人腦,對於大多數人類來說,人腦的結構一樣,但是大家的智商都有差別。

那麼目前世界上的主流CPU由那些呢?我們筆記本上貼的Intel、AMD是怎麼回事呢?下面我們來認識一下;

#1、CPU的分類 我們已經知道CPU內部是含有微指令集的,我們所使用的的軟體都要經過CPU內部的微指令集來完成才行。這些指令集的設計主要又被分為兩種設計理念,這就是目前世界上常見到的兩種主要的CPU種類:分別是精簡指令集(RISC)與複雜指令集(CISC)系統。下面我們就來談談這兩種不同CPU種類的差異! #1.1、精簡指令集 精簡指令集(Reduced Instruction Set Computing,RISC):這種CPU的設計中,微指令集較為精簡,每個指令的執行時間都很短,完成的動作也很單純,指令的執行效能較佳;但是若要做複雜的事情,就要由多個指令來完成。常見的RISC指令集CPU主要例如Sun公司的SPARC系列、IBM公司的Power Architecture(包括PowerPC)系列、與ARM系列等。【注:Sun已經被Oracle收購;】 SPARC架構的計算機常用於學術領域的大型工作站中,包括銀行金融體系的主伺服器也都有這類的計算機架構; PowerPC架構的應用,如Sony出產的Play Station 3(PS3)使用的就是該架構的Cell處理器。 ARM是世界上使用範圍最廣的CPU了,常用的各廠商的手機、PDA、導航系統、網路裝置等,幾乎都用該架構的CPU。 #1.2、複雜指令集 複雜指令集(Complex Instruction Set Computer,CISC)與RISC不同,在CISC的微指令集中,每個小指令可以執行一些較低階的硬體操作,指令數目多而且複雜,每條指令的長度並不相同。因此指令執行較為複雜所以每條指令花費的時間較長,但每條個別指令可以處理的工作較為豐富。常見的CISC微指令集CPU主要有AMD、Intel、VIA等的x86架構的CPU。 由於AMD、Intel、VIA所開發出來的x86架構CPU被大量使用於個人計算機(Personal Computer)上面,因此,個人計算機常被稱為x86架構的計算機!舉個例子,我們在MySQL官網下載MySQL時名字為: Windows(x86,32-bit),ZIP Archive (mysql-5.7.20-win32.zip) 我們發現名字中有x86,這其實就是告訴我們該軟體應用於x86結構的計算機。那麼為何稱為x86架構呢?這是因為最早的那顆Intel發展出來的CPU代號稱為8086,後來依此架構又開發出80285、80386....,因此這種架構的CPU就被稱為x86架構了。 在2003年以前由Intel所開發的x86架構CPU由8位升級到16、32位,後來AMD依此架構修改新一代的CPU為64位,為了區別兩者的差異,因此64位的個人計算機CPU又被統稱為x86_64的架構了。 不同的x86架構的CPU的差別在哪呢?除了CPU的整體結構(如第二層快取、每次運作可執行的指令數等)之外,主要是在於微指令集的不同。新的x86的CPU大多含有很先進的微指令集,這些微指令集可以加速多媒體程式的運作,也能夠加強虛擬化的效能,而且某些微指令集更能夠增加能源效率,讓CPU耗電量降低,這對於高電費是個不錯的訊息。 試想一下,如果CPU的指令集都相同,那麼OS是不是就不用分32bit和64bit了,各種程式的跨平臺是不是就更簡單了呢。 #2 CPU歷史 計算機的發展主要表現在其核心部件——微處理器【微處理器由一片或少數幾片大規模積體電路組成的中央處理器。這些電路執行控制部件和算術邏輯部件的功能。微處理器能完成取指令、執行指令,以及與外界儲存器和邏輯部件交換資訊等操作,是微型計算機的運算控制部分。它可與儲存器和外圍電路晶片組成微型計算機。】的發展上,每當一款新型的微處理器出現時,就會帶動計算機系統的其他部件的相應發展,如計算機體系結構的進一步優化,儲存器存取容量的不斷增大、存取速度的不斷提高,外圍裝置的不斷改進以及新裝置的不斷出現等。根據微處理器的字長和功能,可將其發展劃分為以下幾個階段。 第1階段(1971——1973年)是4位和8位低檔微處理器時代,通常稱為第1代。 第2階段(1974——1977年)是8位中高檔微處理器時代,通常稱為第2代。 第3階段(1978——1984年)是16位微處理器時代,通常稱為第3代。 第4階段(1985——1992年)是32位微處理器時代,又稱為第4代。 第5階段(1993-2005年)是奔騰(pentium)系列微處理器時代,通常稱為第5代。 第6階段(2005年至今)是酷睿(core)系列微處理器時代,通常稱為第6代。“酷睿”是一款領先節能的新型微架構,設計的出發點是提供卓然出眾的效能和能效,提高每瓦特效能,也就是所謂的能效比。 若想具體瞭解CPU歷史參見連結: https://baike.baidu.com/item/%E4%B8%AD%E5%A4%AE%E5%A4%84%E7%90%86%E5%99%A8/284033?fr=aladdin&fromid=368184&fromtitle=%EF%BC%A3%EF%BC%B0%EF%BC%B5#10 總結:CPU按照指令集可以分為精簡指令集CPU和複雜指令集CPU兩種,區別在於前者的指令集精簡,每個指令的執行時間都很短,完成的動作也很單純,指令的執行效能較佳;但是若要做複雜的事情,就要由多個指令來完成。後者的指令集每個小指令可以執行一些較低階的硬體操作,指令數目多而且複雜,每條指令的長度並不相同。因為指令執行較為複雜所以每條指令花費的時間較長,但每條個別指令可以處理的工作較為豐富。 根據位數又可分為32bit和64bit(指的是CPU一次執行指令的資料頻寬),這個具體後面瞭解。CPU往往又可細分為運算器和控制器兩部分,下面我們再來敘說一下這兩部分。 #2.1、運算器 運算器是對資訊進行處理和運算的部件。經常進行的運算是算術運算和邏輯運算,所以運算器又可稱為算術邏輯運算部件(Arithmetic and Logical,ALU)。 運算器的核心是加法器。運算器中還有若干個通用暫存器或累加暫存器,用來暫存運算元並存放運算結果。暫存器的存取速度比儲存器的存放速度快很多。關於暫存器,我們在後面介紹CPU的時候再認識。 #2.2 控制器 控制器是整個計算機的指揮中心,它的主要功能是按照人們預先確定的操作步驟,控制整個計算機的各部件有條不紊的自動工作。 控制器從主存中逐條地讀取出指令進行分析,根據指令的不同來安排操作順序,向各部件發出相應的操作訊號,控制它們執行指令所規定的任務。 控制器中包括一些專用的暫存器。

因訪問記憶體以得到指令或資料的時間比cpu執行指令花費的時間要長得多,所以,所有CPU內部都有一些用來儲存關鍵變數和臨時資料的暫存器,這樣通常在cpu的指令集中專門提供一些指令,用來將一個字(可以理解為資料)從記憶體調入暫存器,以及將一個字從暫存器存入記憶體。cpu其他的指令集可以把來自暫存器、記憶體的運算元據組合,或者用兩者產生一個結果,比如將兩個字相加並把結果存在暫存器或記憶體中。 暫存器的分類: 1.除了用來儲存變數和臨時結果的通用暫存器外 2.多數計算機還有一些對程式設計師課件的專門暫存器,其中之一便是程式計數器,它儲存了將要取出的下一條指令的記憶體地址。在指令取出後,程式計算器就被更新以便執行後期的指令 3.另外一個暫存器便是堆疊指標,它指向記憶體中當前棧的頂端。該棧包含已經進入但是還沒有退出的每個過程中的一個框架。在一個過程的堆疊框架中儲存了有關的輸入引數、區域性變數以及那些沒有儲存在暫存器中的臨時變數 4.最後 一個非常重要的暫存器就是程式狀態字暫存器(Program Status Word,PSW),這個暫存器包含了條碼位(由比較指令設定)、CPU優先順序、模式(使用者態或核心態),以及各種其他控制位。使用者通常讀入整個PSW,但是隻對其中少量的欄位寫入。在系統呼叫和I/O中,PSW非常非常非常非常非常非常重要 暫存器的維護: 作業系統必須知曉所有的暫存器。在時間多路複用的CPU中,作業系統會經常中止正在執行的某個程式並啟動(或再次啟動)另一個程式。每次停止一個執行著的程式時,作業系統必須儲存所有的暫存器,這樣在稍後該程式被再次執行時,可以把這些暫存器重新裝入。

處理器設計的演變

1.最開始取值、解碼、執行這三個過程是同時進行的,這意味著任何一個過程完成都需要等待其餘兩個過程執行完畢,時間浪費

2.後來被設計成了流水線式的設計,即執行指令n時,可以對指令n+1解碼,並且可以讀取指令n+2,完全是一套流水線。

3.超變數cpu,比流水線更加先進,有多個執行單元,可以同時負責不同的事情,比如看片的同時,聽歌,打遊戲。

兩個或更多的指令被同時取出、解碼並裝入一個保持緩衝區中,直至它們都執行完畢。只有有一個執行單元空閒,就檢查保持緩衝區是否還有可處理的指令

這種設計存在一種缺陷,即程式的指令經常不按照順序執行,在多數情況下,硬體負責保證這種運算結果與順序執行的指令時的結果相同。

核心態與使用者態

除了在嵌入式系統中的非常簡答的CPU之外,多數CPU都有兩種模式,即核心態與使用者態。 通常,PSW中有一個二進位制位控制這兩種模式。 核心態:當cpu在核心態執行時,cpu可以執行指令集中所有的指令,很明顯,所有的指令中包含了使用硬體的所有功能,(作業系統在核心態下執行,從而可以訪問整個硬體) 使用者態:使用者程式在使用者態下執行,僅僅只能執行cpu整個指令集的一個子集,該子集中不包含操作硬體功能的部分,因此,一般情況下,在使用者態中有關I/O和記憶體保護(作業系統佔用的記憶體是受保護的,不能被別的程式佔用),當然,在使用者態下,將PSW中的模式設定成核心態也是禁止的。 核心態與使用者態切換 使用者態下工作的軟體不能操作硬體,但是我們的軟體比如暴風影音,一定會有操作硬體的需求,比如從磁碟上讀一個電影檔案,那就必須經歷從使用者態切換到核心態的過程,為此,使用者程式必須使用系統呼叫(system call),系統呼叫陷入核心並呼叫作業系統,TRAP指令把使用者態切換成核心態,並啟用作業系統從而獲得服務。 請把的系統呼叫看成一個特別的的過程呼叫指令就可以了,該指令具有從使用者態切換到核心態的特別能力。

多執行緒和多核晶片

moore定律指出,晶片中的電晶體數量每18個月翻一倍,隨著電晶體數量的增多,更強大的功能稱為了可能,如

I.第一步增強:在cpu晶片中加入更大的快取,一級快取L1,用和cpu相同的材質製成,cpu訪問它沒有時延

II.第二步增強:一個cpu中的處理邏輯增多,intel公司首次提出,稱為多執行緒(multithreading)或超執行緒(hyperthreading),對使用者來說一個有兩個執行緒的cpu就相當於兩個cpu,我們後面要學習的程式和執行緒的知識就起源於這裡,程式是資源單位而執行緒才是cpu的執行單位。

多執行緒執行cpu保持兩個不同的執行緒狀態,可以在納秒級的時間內來回切換,速度快到你看到的結果是併發的,偽並行的,然而多執行緒不提供真正的並行處理,一個cpu同一時刻只能處理一個程式(一個程式中至少一個執行緒)

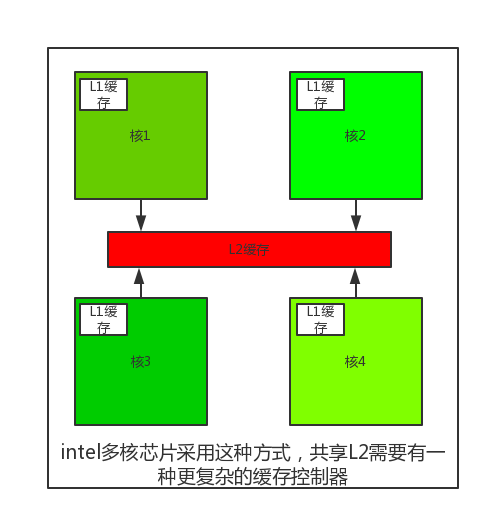

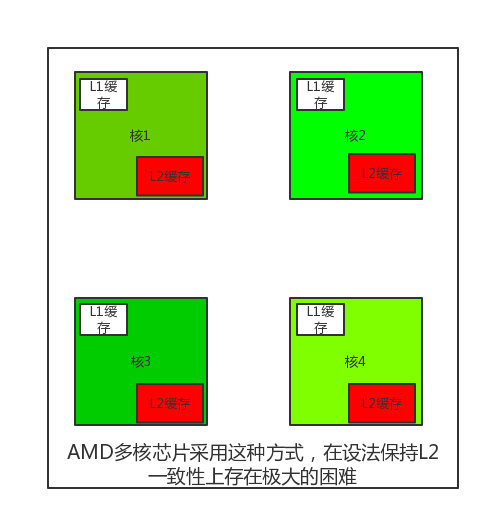

III.第三步增強:除了多執行緒,還出現了傲寒2個或者4個完整處理器的cpu晶片,如下圖。要使用這類多核晶片肯定需要有多處理作業系統

4.2 儲存器

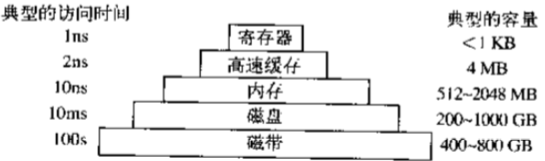

計算機中第二重要的就是儲存了,所有人都意淫著儲存:速度快(這樣cpu的等待儲存器的延遲就降低了)+容量大+價錢便宜。然後同時兼備三者是不可能的,所以有了如下的不同的處理方式

儲存器系統採用如上圖的分層結構,頂層的儲存器速度較高,容量較小,與底層的儲存器相比每位的成本較高,其差別往往是十億數量級的

暫存器即L1快取:

用與cpu相同材質製造,與cpu一樣快,因而cpu訪問它無時延,典型容量是:在32位cpu中為32*32,在64位cpu中為64*64,在兩種情況下容量均<1KB。

快取記憶體即L2快取:

主要由硬體控制快取記憶體的存取,記憶體中有快取記憶體行按照0~64位元組為行0,64~127為行1。。。最常用的快取記憶體行放置在cpu內部或者非常接近cpu的快取記憶體中。當某個程式需要讀一個儲存字時,快取記憶體硬體檢查所需要的快取記憶體行是否在快取記憶體中。如果是,則稱為快取記憶體命中,快取滿足了請求,就不需要通過匯流排把訪問請求送往主存(記憶體),這畢竟是慢的。快取記憶體的命中通常需要兩個時鐘週期。快取記憶體為命中,就必須訪問記憶體,這需要付出大量的時間代價。由於快取記憶體價格昂貴,所以其大小有限,有些機器具有兩級甚至三級快取記憶體,每一級快取記憶體比前一級慢但是容易大。

快取在電腦科學的許多領域中起著重要的作用,並不僅僅只是RAM(隨機存取儲存器)的快取行。只要存在大量的資源可以劃分為小的部分,那麼這些資源中的某些部分肯定會比其他部分更頻發地得到使用,此時用快取可以帶來效能上的提升。一個典型的例子就是作業系統一直在使用快取,比如,多數作業系統在記憶體中保留頻繁使用的檔案(的一部分),以避免從磁碟中重複地呼叫這些檔案,類似的/root/a/b/c/d/e/f/a.txt的長路徑名轉換成該檔案所在的磁碟地址的結果然後放入快取,可以避免重複尋找地址,還有一個web頁面的url地址轉換為網路地址(IP)地址後,這個轉換結果也可以快取起來供將來使用。

快取是一個好方法,在現代cpu中設計了兩個快取,再看4.1中的兩種cpu設計圖。第一級快取稱為L1總是在CPU中,通常用來將已經解碼的指令調入cpu的執行引擎,對那些頻繁使用的資料自,多少晶片還會按照第二L1快取 。。。另外往往設計有二級快取L2,用來存放近來經常使用的記憶體字。L1與L2的差別在於對cpu對L1的訪問無時間延遲,而對L2的訪問則有1-2個時鐘週期(即1-2ns)的延遲。

記憶體:

再往下一層是主存,此乃儲存器系統的主力,主存通常稱為隨機訪問儲存RAM,就是我們通常所說的記憶體,容量一直在不斷攀升,所有不能再快取記憶體中找到的,都會到主存中找,主存是易失性儲存,斷電後資料全部消失

除了主存RAM之外,許多計算機已經在使用少量的非易失性隨機訪問儲存如ROM(Read Only Memory,ROM),在電源切斷之後,非易失性儲存的內容並不會丟失,ROM只讀儲存器在工廠中就被程式設計完畢,然後再也不能修改。ROM速度快且便宜,在有些計算機中,用於啟動計算機的引導載入模組就存放在ROM中,另外一些I/O卡也採用ROM處理底層裝置的控制。

EEPROM(Electrically Erasable PROM,電可擦除可程式設計ROM)和快閃記憶體(flash memory)也是非易失性的,但是與ROM相反,他們可以擦除和重寫。不過重寫時花費的時間比寫入RAM要多。在行動式電子裝置中中,快閃記憶體通常作為儲存媒介。快閃記憶體是數碼相機中的膠捲,是行動式音譯播放器的磁碟,還應用於固態硬碟。快閃記憶體在速度上介於RAM和磁碟之間,但與磁碟不同的是,快閃記憶體擦除的次數過多,就被磨損了。

還有一類儲存器就是CMOS,它是易失性的,許多計算機利用CMOS儲存器來保持當前時間和日期。CMOS儲存器和遞增時間的電路由一小塊電池驅動,所以,即使計算機沒有加電,時間也仍然可以正確地更新,除此之外CMOS還可以儲存配置的引數,比如,哪一個是啟動磁碟等,之所以採用CMOS是因為它耗電非常少,一塊工廠原裝電池往往能使用若干年,但是當電池失效時,相關的配置和時間等都將丟失

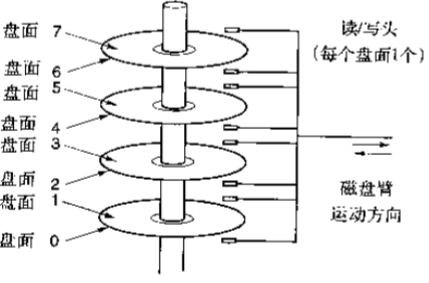

4.3 磁碟

磁碟低速的原因是因為它一種機械裝置,在磁碟中有一個或多個金屬碟片,它們以5400,7200或10800rpm(RPM =revolutions per minute 每分鐘多少轉 )的速度旋轉。從邊緣開始有一個機械臂懸在盤面上,這類似於老式黑膠唱片機上的拾音臂。資訊解除安裝磁碟上的一些列的同心圓上,是一連串的2進位制位(稱為bit位),為了統計方法,8個bit稱為一個位元組bytes,1024bytes=1k,1024k=1M,1024M=1G,所以我們平時所說的磁碟容量最終指的就是磁碟能寫多少個2進位制位。

每個磁頭可以讀取一段換新區域,稱為磁軌

把一個戈丁手臂位置上所以的磁軌合起來,組成一個柱面

每個磁軌劃成若干扇區,扇區典型的值是512位元組

資料都存放於一段一段的扇區,即磁軌這個圓圈的一小段圓圈,從磁碟讀取一段資料需要經歷尋道時間和延遲時間

平均尋道時間

機械手臂從一個柱面隨機移動到相鄰的柱面的時間成為尋到時間,找到了磁軌就以為著招到了資料所在的那個圈圈,但是還不知道資料具體這個圓圈的具體位置

4.4 磁帶

在價錢相同的情況下比硬碟擁有更高的儲存容量,雖然速度低於磁碟,但是因其大容量,在地震水災火災時可移動性強等特性,常被用來做備份。(常見於大型資料庫系統中)

4.5 I/O裝置

cpu和儲存器並不是作業系統唯一需要管理的資源,I/O裝置也是非常重要的一環。

見四中的圖,I/O裝置一般包括兩個部分:裝置控制器和裝置本身。

控制器:是查詢主機板上的一塊晶片或一組晶片(硬碟,網路卡,音效卡等都需要插到一個口上,這個口連的便是控制器),控制器負責控制連線的裝置,它從作業系統接收命令,比如讀硬碟資料,然後就對硬碟裝置發起讀請求來讀出內容。

控制器的功能:通常情況下對裝置的控制是非常複雜和具體的,控制器的任務就是為作業系統遮蔽這些複雜而具體的工作,提供給作業系統一個簡單而清晰的介面

裝置本身:有相對簡單的介面且標準的,這樣大家都可以為其編寫驅動程式了。要想呼叫裝置,必須根據該介面編寫複雜而具體的程式,於是有了控制器提供裝置驅動介面給作業系統。必須把裝置驅動程式安裝到作業系統中。

4.5 輸入輸出裝置

#1、輸入裝置 輸入裝置的任務是把人們編好的程式和原始資料送到計算機中去,並且將他們轉換成計算機記憶體所能識別和接受的資訊方式。 安輸入資訊的形態可分為字元(包括漢字)輸入、圖形輸入、影象輸入及語言輸入等。目前,常見的輸入裝置有:鍵盤、滑鼠、掃描器等。輔助儲存器(磁碟、磁帶)也可以看作輸入裝置。另外,自動控制和檢測系統中使用的模數(A/D)轉換裝置也是一種輸入裝置。 #2、輸出裝置 輸出裝置的任務是將計算機的處理結果以人或其他裝置所能接受的形式送出計算機。 目前最常用的輸出裝置是印表機和顯示器。輔助儲存器也可以看做輸出裝置。另外,數模(D/A)轉換裝置也是一種輸出裝置。

4.6 匯流排

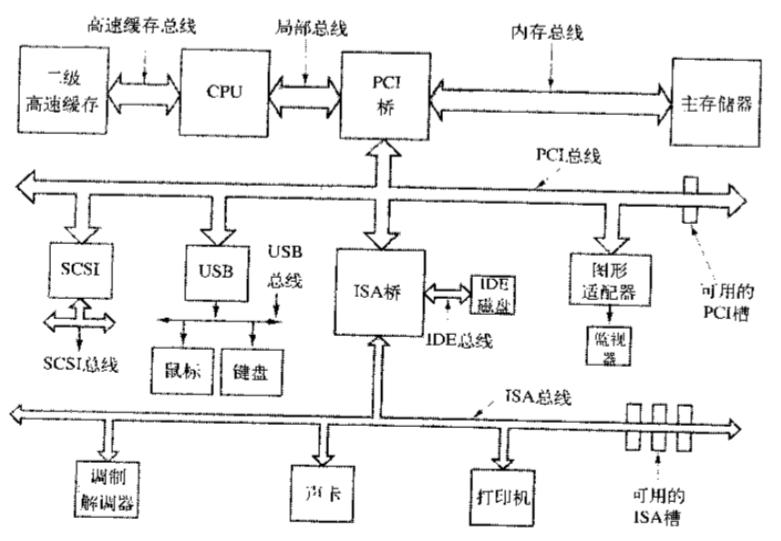

四小節中的結構在小型計算機中沿用了多年,並也用在早期的IBM PC中。但是隨著處理器和儲存器速度越來越快,單匯流排很難處理匯流排的交通流量了,於是出現了下圖的多匯流排模式,他們處理I/O裝置及cpu到儲存器的速度都更快。

北橋即PCI橋:連線高速裝置

南橋即ISA橋:連線慢速裝置

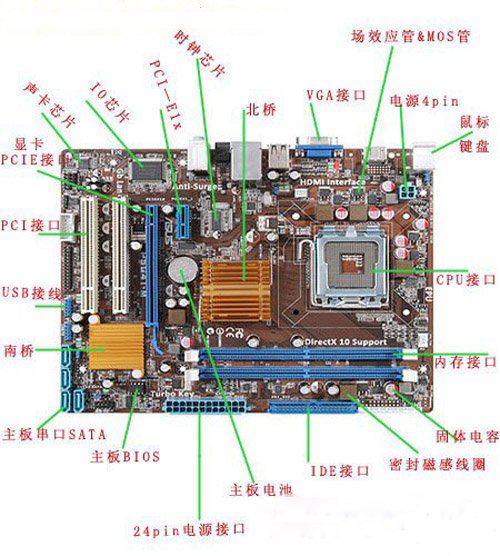

主機板圖解:

電源(Power)==心臟:所有的元件要能運作,得要有足夠的電力供給才行。這就好像心臟一樣,如果心臟不跳動了,人就嗝屁了,電腦也是如果沒有電源,那也就是一堆垃圾,什麼作用都沒有。

4.7 啟動計算機

在計算機的主機板上有一個基本的輸入輸出程式(Basic Input Output system)

BIOS就相當於一個小的作業系統,它有底層的I/O軟體,包括讀鍵盤,寫螢幕,進行磁碟I/O,該程式存放於一非易失性快閃記憶體RAM中。

啟動流程

1.計算機加電

2.BIOS開始執行,檢測硬體:cpu、記憶體、硬碟等

3.BIOS讀取CMOS儲存器中的引數,選擇啟動裝置

4.從啟動裝置上讀取第一個扇區的內容(MBR主開機記錄512位元組,前446為引導資訊,後64為分割槽資訊,最後兩個為標誌位)

5.根據分割槽資訊讀入bootloader啟動裝載模組,啟動作業系統

6.然後作業系統詢問BIOS,以獲得配置資訊。對於每種裝置,系統會檢查其裝置驅動程式是否存在,如果沒有,系統則會要求使用者按照裝置驅動程式。一旦有了全部的裝置驅動程式,作業系統就將它們調入核心。然後初始有關的表格(如程式表),穿件需要的程式,並在每個終端上啟動登入程式或GUI