是取樣速率低於5Msps (每秒百萬次取樣)的中等至高解析度應用的常見結構。

SAR ADC的解析度一般為8位至16位,具有低功耗、小尺寸等特點。

這些特點使該型別ADC具有很寬的應用範圍,例如便攜/電池供電儀表、筆輸入量化器、工業控制和資料/訊號採集等。

顧名思義,SAR ADC實質上是實現一種二進位制搜尋演算法。

所以,當內部電路執行在數兆赫茲(MHz)時,由於逐次逼近演算法的緣故,ADC取樣速率僅是該數值的幾分之一。

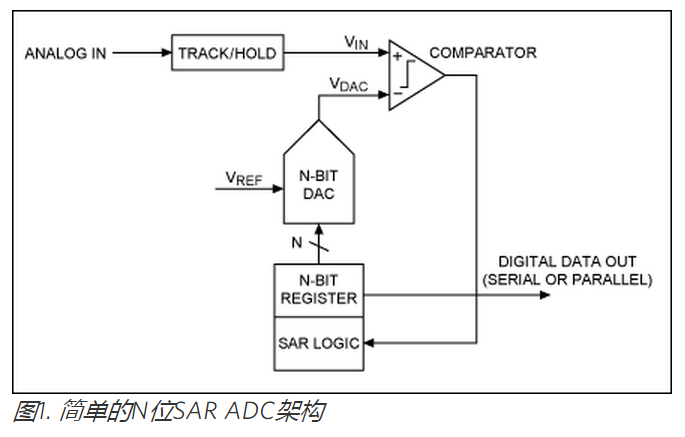

SAR ADC的架構

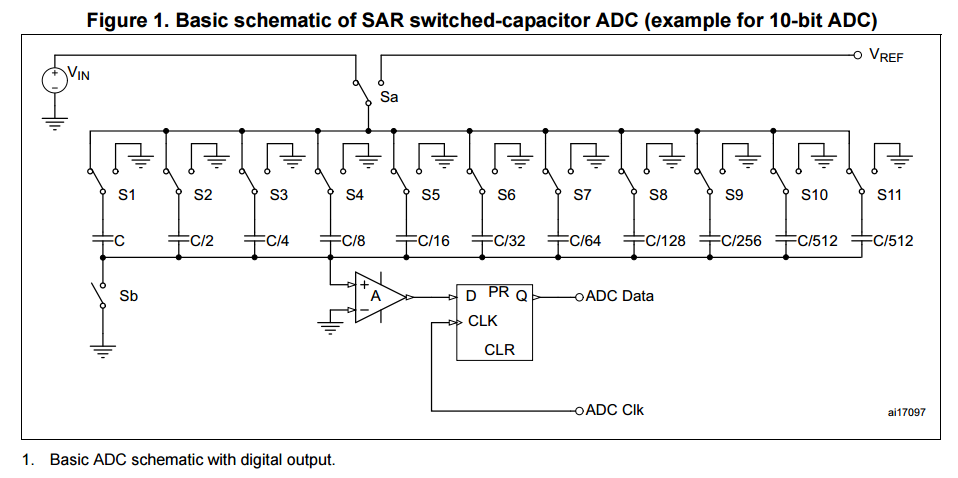

儘管實現SAR ADC的方式千差萬別,但其基本結構非常簡單(見圖1)。

模擬輸入電壓(VIN)由取樣/保持電路保持。

為實現二進位制搜尋演算法,N位暫存器首先設定在中間刻度(即:100... .00,MSB設定為1)。

這樣,DAC輸出(VDAC)被設為VREF/2,VREF是提供給ADC的基準電壓。

然後,比較判斷VIN是小於還是大於VDAC。

如果VIN大於VDAC,則比較器輸出邏輯高電平或1,N位暫存器的MSB保持為1。

相反,如果VIN小於VDAC,則比較器輸出邏輯低電平,N位暫存器的MSB清0。

隨後,SAR控制邏輯移至下一位,並將該位設定為高電平,進行下一次比較。

這個過程一直持續到LSB。上述操作結束後,也就完成了轉換,N位轉換結果儲存在暫存器內。

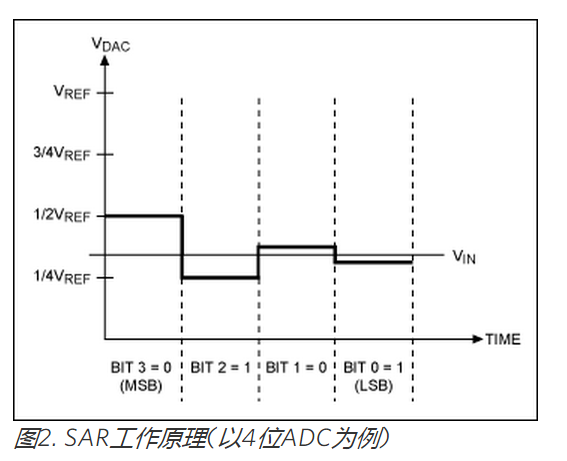

圖2給出了一個4位轉換示例,y軸(和圖中的粗線)表示DAC的輸出電壓。

本例中,第一次比較表明VIN < VDAC。所以,位3置為0。

然後DAC被置為0100,並執行第二次比較。由於VIN > VDAC,位2保持為1。

DAC置為0110,執行第三次比較。根據比較結果,位1置0,

DAC又設定為0101,執行最後一次比較。

最後,由於VIN > VDAC,位0確定為1。

注意,對於4位ADC需要四個比較週期。

通常,N位SAR ADC需要N個比較週期,在前一位轉換完成之前不得進入下一次轉換。

由此可以看出,該類ADC能夠有效降低功耗和空間,當然,也正是由於這個原因,

解析度在14位至16位,速率高於幾Msps (每秒百萬次取樣)的逐次逼近ADC極其少見。

SAR ADC的另一個顯著的特點是:功耗隨取樣速率而改變。

這一點與閃速ADC或流水線ADC不同,後者在不同的取樣速率下具有固定的功耗。

這種可變功耗特性對於低功耗應用或者不需要連續採集資料的應用非常有利(例如,用於PDA 數字轉換器)。

SAR的深入分析

SAR ADC的兩個重要部件是比較器和DAC,稍後我們可以看到,

圖1中取樣/保持電路可以嵌入到DAC內,不作為一個獨立的電路。

SAR ADC的速度受限於:

- DAC的建立時間,在這段時間內必須穩定在整個轉換器的解析度以內(如:½ LSB)

- 比較器,必須在規定的時間內能夠分辨VIN與VDAC的微小差異

- 邏輯開銷

DAC

DAC的最大建立時間通常取決於其MSB的建立時間,原因很簡單,MSB的變化代表了DAC輸出的最大偏移。

另外,ADC的線性也受DAC線性指標的限制。因此,由於元件固有匹配度的限制,

解析度高於12位的SAR ADC常常需要調理或校準,以改善其線性指標。

雖然這在某種程度上取決於處理工藝和設計,但在實際的DAC設計中,元件的匹配度將線性指標限制在12位左右。

許多SAR ADC採用具有固有采樣/保持功能的電容式DAC。

電容式DAC根據電荷再分配的原理產生模擬輸出電壓,由於這種型別的DAC在SAR ADC中很常用,所以,我們最好討論一下它們的工作原理。

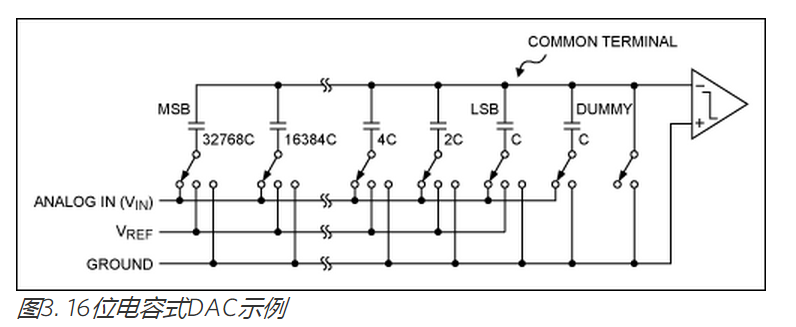

電容式DAC包括一個由N個按照二進位制加權排列的電容和一個“空LSB”電容組成的陣列。

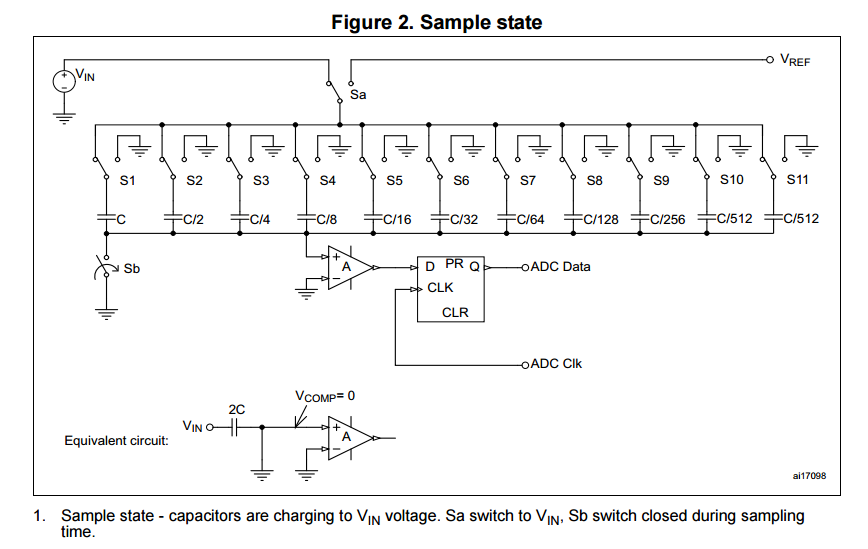

圖3是一個16位電容式DAC與比較器相連線的範例。取樣階段,陣列的公共端(所有電容連線的公共點,見圖3)接地,

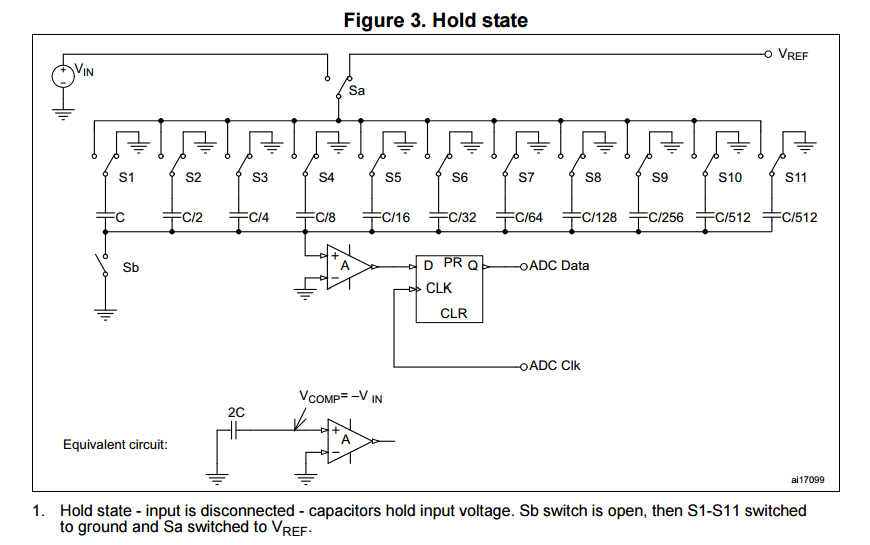

所有自由端連線到輸入訊號(模擬輸入或VIN)。取樣後,公共端與地斷開,自由端與VIN斷開,在電容陣列上有效地獲得了與輸入電壓成比例的電荷量。

然後,將所有電容的自由端接地,驅動公共端至一個負壓-VIN。

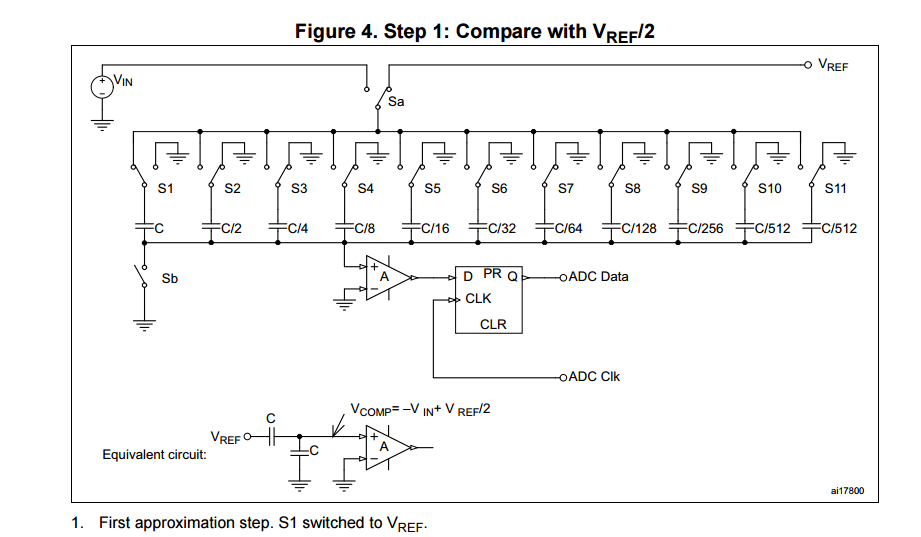

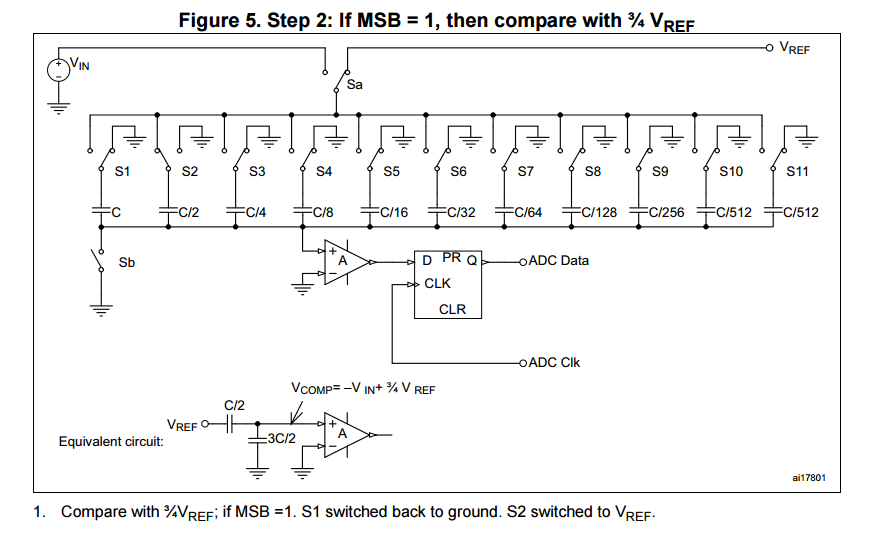

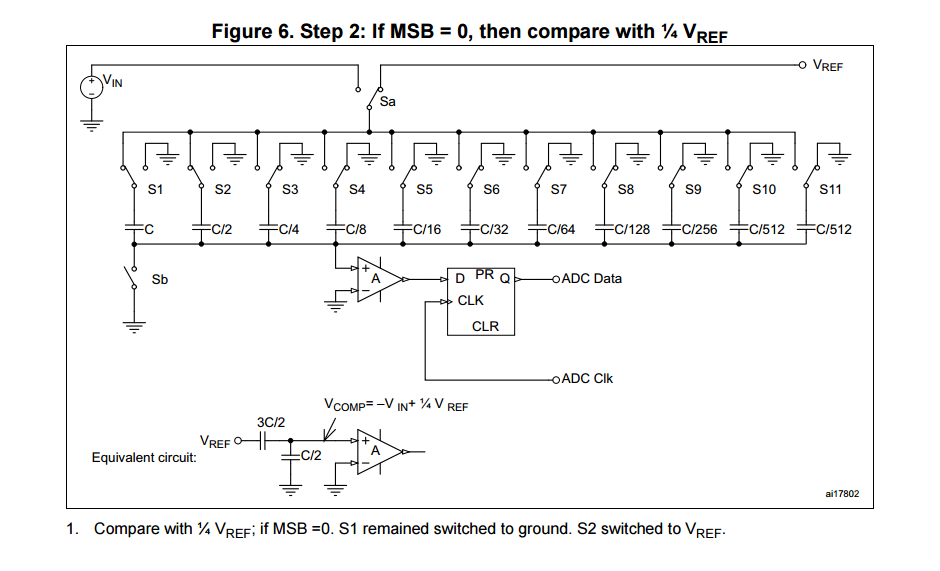

作為二進位制搜尋演算法的第一步,MSB電容的底端與地斷開並連線到VREF,驅動公共端電壓向正端移動½VREF。

因此,VCOMMON = -VIN + ½ × VREF

如果VCOMMON < 0 (即VIN > ½ × VREF),比較器輸出為邏輯1。如果VIN < ½ × VREF,比較器輸出為邏輯0。

如果比較器輸出為邏輯1,MSB電容的底端保持連線至VREF。否則,MSB電容的底端連線至地。

接下來,下一個較小電容的底端連線至VREF,將新的VCOMMON電壓與地電位進行比較。

繼續上述過程,直至所有位的值均確定下來。

簡言之,VCOMMON = -VIN + BN-1 × VREF/2 + BN-2 × VREF/4 + BN-1 × VREF/8 + ... + B0 × VREF/2N-1 (B_為比較器輸出/ADC輸出位)。

比較器

比較器需要具有足夠的速度和精度,儘管比較器的失調電壓不影響整體的線性度,

它將給系統傳輸特性曲線帶來一個偏差,為減小比較器的失調電壓引入了失調消除技術。

然而,還必須考慮噪聲,比較器的等效輸入噪聲通常要設計在1 LSB以內。

比較器必須能夠分辨出整個系統精度以內的電壓,也就是說比較器需要保證與系統相當的精度。

SAR ADC與其它ADC結構的比較

與流水線ADC相比

流水線ADC採用一種並行結構,並行結構中的每一級同時進行一位或幾位的逐次取樣。

這種固有的並行結構提高了資料的吞吐率,但要以功耗和延遲為代價。

所謂延遲,在此情況下定義為ADC取樣到模擬輸入的時間與輸出端得到量化資料的時間差。

例如,一個5級流水線ADC至少存在5個時鐘週期的延遲,而SAR只有1個時鐘週期的延遲。

需要注意的是,延遲的定義只是相對於ADC的吞吐率而言,並非指SAR的內部時鐘,該時鐘是吞吐率的許多倍。

流水線ADC需要頻繁地進行數字誤差校準,以降低對流水線上每一級閃速ADC (即比較器)的精度要求。

而SAR ADC的比較器精度只需與整體系統的精度相當即可。

流水線ADC一般比同等級別的SAR需要更多的矽片面積。

與SAR一樣,精度高於12位的流水線ADC通常需要一些某種形式的微調或校準。

與閃速ADC相比

閃速ADC由大量的比較器構成,每個比較器包括一個寬頻、低增益預放大器和鎖存器。

預放大器必須僅用於提供增益,不需要高線性度和高精度,這意味著只有比較器的門限值才需具有較高的精度。

所以,閃速ADC是目前轉換速率最快的一種架構。

通常需要折衷考慮閃速ADC的速度以及SAR DAC的低功耗和小尺寸特性。

儘管極高速的8位閃速ADC (以及它們的摺疊/內插變種)具有高達1.5Gsps的取樣速率,但很難找到10位的閃速ADC,

而12位(及更高位)閃速ADC還沒有商用化的產品。

這是由於解析度每提高1位,閃速ADC中比較器的個數將成倍增長,同時還要保證比較器的精度是系統精度的兩倍。

而在SAR ADC中,提高解析度需要更精確的元件,但複雜度並非按指數率增長。

當然,SAR ADC的速度是無法與閃速ADC相比較的。

與Σ-Δ轉換器相比

傳統的過取樣/Σ-Δ轉換器被普遍用於頻寬限制在大約22kHz的數字音訊應用。

近來,一些寬頻Σ-Δ轉換器能夠達到1MHz至2MHz的頻寬,解析度在12位至16位。

這通常由高階Σ-Δ調製器(例如,4階或更高)配合一個多位ADC和多位反饋DAC構成。

Σ-Δ轉換器具有一個優於SAR ADC的先天優勢:

即不需要特別的微調或校準,即使解析度達到16位至18位。

由於該型別ADC的取樣速率要比有效頻寬高得多,因此也不需要在模擬輸入端增加快速滾降的抗混疊濾波器。

由後端數字濾波器進行處理。Σ-Δ轉換器的過取樣特性還可用來“平滑”模擬輸入中的任何系統噪聲。

Σ-Δ轉換器要以速率換取解析度。由於產生一個最終取樣需要取樣很多次(至少是16倍,一般會更多),

這就要求Σ-Δ調製器的內部類比電路的工作速率要比最終的資料速率快很多。

數字抽取濾波器的設計也是一個挑戰,並要消耗相當大的矽片面積。

在不遠的將來,速度最高的高解析度Σ-Δ轉換器的頻寬將不大可能高出幾兆赫茲很多。

總結

綜上所述,SAR ADC的主要優點是低功耗、高解析度、高精度、以及小尺寸。

由於這些優勢,SAR ADC常常與其它更大的功能整合在一起。

SAR結構的主要侷限是取樣速率較低,並且其中的各個單元(如DAC和比較器),需要達到與整體系統相當的精度。

The ADC in STM32x microcontrollers uses the SAR (successive approximation register) principle,

by which the conversion is performed in several steps.

The number of conversion steps is equal to the number of bits in the ADC converter.

Each step is driven by the ADC clock.

Each ADC clock produces one bit from result to output.

ADC internal design is a switched-capacitor type.

The following figures (Figure 1 to Figure 6) explain the principle of ADC operation.

The example given below shows only the first steps of approximation

but the process continues till the LSB is reached.