記憶體定址(一)硬體定址的基本原理:硬體中的分段和分頁機制,控制暫存器CR0與CR3

摘要:本文講述8086怎樣進行晶片級別的記憶體定址,linux又是如何在這些硬體的基礎上進行定址的。本文主要討論硬體和linux定址的基本原理,後續將討論分頁機制的具體實現,核心如何給自己分配主存,怎樣給程式分配線性地址。

一、定址流程

邏輯地址經過分段單元形成線性地址,然後經過分頁單元形成實體地址。

二、硬體中的分段

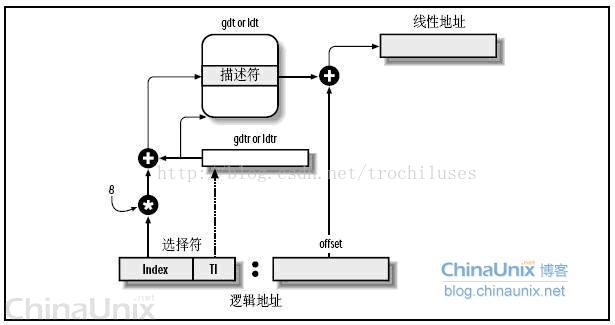

1.段選擇符和段暫存器

32位的邏輯地址包含16位的段選擇符和36位的偏移量。處理器的段暫存器用於存放段選擇符。其中cs暫存器有一個重要功能:指明當前特權級。

2.段描述符

每個段由8位的段描述符表示,存放在GDT和LDT中,GDT和LDT在主存中的位置和大小存放在gdtr和ldtr暫存器中。

關於段選擇符和段描述符,可以參考:保護模式程式設計之(一)——分段機制與GDT/LDThttp://blog.csdn.net/trochiluses/article/details/8968750

快速訪問段描述符

每當一個段選擇符被裝入暫存器的時候,相應的段描述符號就從記憶體裝入相應的非程式設計CPU暫存器,從此,邏輯地址的轉換不經過主存中的GDT或者LDT而是直接應用相關CPU暫存器即可。只有暫存器內容發生改變,才會訪問GDT或者LDT。

3.分段單元

邏輯地址的轉換過程如下:

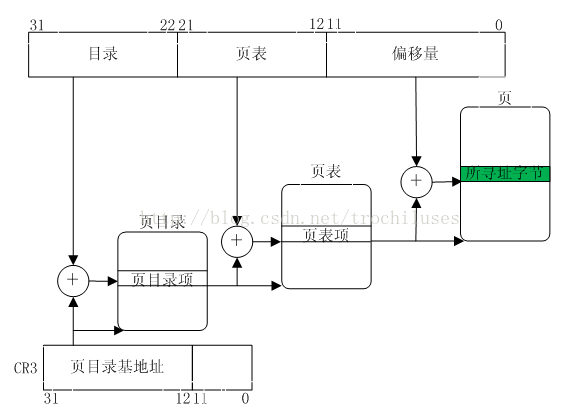

三、硬體中的分頁

i386 CPU實現記憶體管理的基本思路是通過頁目錄和頁表兩極對映實現從線性地址到實體地址的轉換。原因:4GB的線性地址空間,如果我們採用一級對映,頁大小是4K,那麼需要的頁表項數量為4G/4K=1M;另外,一個頁表項的大小是8B,如此一個程式的頁表需要的儲存空間位8M。實際情況下,可能線性地址空間僅僅某一部分有效(例如0x00000000~0x0000ffff),此時如果採用二級頁表,可以避免一些無用線性地址的對映(如果相應的線性地址無效,那麼對應的頁目錄項設定為空)。

其中暫存器cr3用於存放當前程式正在使用的頁目錄基地址。dir用於指明目錄項,table用於指明表項,offset用於指明頁內偏移。8086處理器分頁原理如下圖:

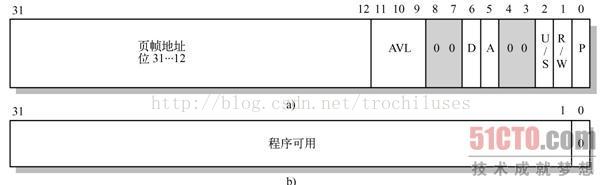

頁目錄項和頁表項有同樣的結構;

它們都有4B共32b,具體佈局如下:

其中每個位的作用如下:

P--位0是存在(Present)標誌,用於指明表項對地址轉換是否有效。P=1表示有效;P=0表示無效。在頁轉換過程中,如果說涉及的頁目錄或頁表的表項無效,則會導致一個異常。如果P=0,那麼除表示表項無效外,其餘位可供程式自由使用,如圖4-18b所示。例如,作業系統可以使用這些位來儲存已儲存在磁碟上的頁面的序號。

R/W--位1是讀/寫(Read/Write)標誌。如果等於1,表示頁面可以被讀、寫或執行。如果為0,表示頁面只讀或可執行。當處理器執行在超級使用者特權級(級別0、1或2)時,則R/W位不起作用。頁目錄項中的R/W位對其所對映的所有頁面起作用。

U/S--位2是使用者/超級使用者(User/Supervisor)標誌。如果為1,那麼執行在任何特權級上的程式都可以訪問該頁面。如果為0,那麼頁面只能被執行在超級使用者特權級(0、1或2)上的程式訪問。頁目錄項中的U/S位對其所對映的所有頁面起作用。

A--位5是已訪問(Accessed)標誌。當處理器訪問頁表項對映的頁面時,頁表表項的這個標誌就會被置為1。當處理器訪問頁目錄表項對映的任何頁面時,頁目錄表項的這個標誌就會被置為1。處理器只負責設定該標誌,作業系統可通過定期地復位該標誌來統計頁面的使用情況。

D--位6是頁面已被修改(Dirty)標誌。當處理器對一個頁面執行寫操作時,就會設定對應頁表表項的D標誌。處理器並不會修改頁目錄項中的D標誌。

AVL--該欄位保留專供程式使用。處理器不會修改這幾位,以後的升級處理器也不會。

PAGE SIZE只用於頁目錄項,如果為1表示啟用大頁,2M或者4M

四、控制暫存器CR0與CR3

相關文章

- Linux記憶體定址之分段機制Linux記憶體

- Linux 記憶體定址之分段機制Linux記憶體

- Linux記憶體定址之分頁機制Linux記憶體

- Linux 記憶體定址之分頁機制Linux記憶體

- 暫存器定址和暫存器間接定址的區別

- 記憶體定址原理記憶體

- x64 結構體系下的記憶體定址結構體記憶體

- 80386的分段機制、分頁機制和實體地址的形成

- 作業系統(八) -- 記憶體的分段與分頁作業系統記憶體

- 80386分頁機制與虛擬記憶體記憶體

- 計算機的硬體與軟體計算機

- 計算機的硬體系統儲存器計算機

- win10為硬體保留的記憶體怎麼釋放 win10取消為硬體保留的記憶體怎麼操作Win10記憶體

- Java的記憶體管理機制之記憶體區域劃分Java記憶體

- 計算機儲存器容量和定址能力的關係計算機

- 為硬體保留記憶體 問題的解決方法記憶體

- 記一次 rr 和硬體斷點解決記憶體踩踏問題斷點記憶體

- NIO的JVM記憶體和機器記憶體的選擇JVM記憶體

- 為什麼暫存器比記憶體快?記憶體

- 【記憶體管理】頁面分配機制記憶體

- Windows記憶體管理-分段Windows記憶體

- win10取消為硬體保留記憶體的解決方法Win10記憶體

- Redis的記憶體和實現機制Redis記憶體

- VbScript獲取本地機器的硬體配置

- 80386學習(五) 80386分頁機制與虛擬記憶體記憶體

- Redis的記憶體回收機制和記憶體過期淘汰策略詳解Redis記憶體

- Java的記憶體回收機制Java記憶體

- RFID讀寫器的組成,軟體與硬體部分

- Objective-C中的記憶體管理機制Object記憶體

- 共享記憶體分段問題記憶體

- javascript的垃圾回收機制和記憶體管理JavaScript記憶體

- 3. 暫存器(記憶體) | 問題 3.7 - 3.10記憶體

- 在繼承和多型中的記憶體分配機制繼承多型記憶體

- Linux的記憶體分頁管理Linux記憶體

- Linux 的記憶體分頁管理Linux記憶體

- JavaScript 記憶體機制JavaScript記憶體

- 程式的機器級表示:定址方式、指令及棧的執行機制

- 智慧硬體的商機——資訊圖