我們有幸請到了UCLA的PhD KO大神來為我們介紹一些sense amplifier的insight,本系列可以作為電路大師課系列電路大師課系列-模擬積體電路設計第四講:基本π網路(上)的課外讀物 :)

讀出放大器簡介

儲存器是用於儲存資訊的記憶裝置,如隨機儲存器(RAM)、磁碟(disk)、快閃記憶體(Flash)等儲存器均在計算機系統中得到廣泛應用。讀出延遲,功耗,面積/位,和價格/位都屬於儲存器的重要指標(顯然,你不希望自己的手機因為儲存器而續航低,價格貴,速度慢)。讀出放大器是儲存器電路的一個重要組成部分,它屬於讀出電路的一部分(顯然,所有儲存器都要支援讀出操作)。讀出放大器的使用恰恰可以大大降低讀出延遲和讀出功耗,同時與其他降低延遲的功耗的方法相比面積代價較小。

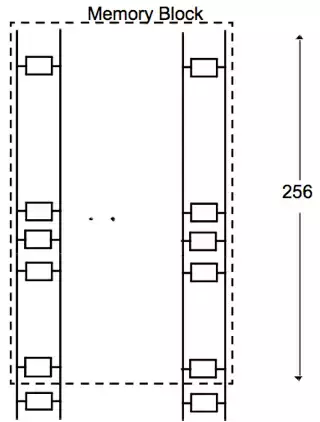

SRAM位線結構;

我們以一個典型的靜態隨機儲存器(SRAM)為例,來說明讀出放大器的重要性和效能指標要求。如圖是SRAM的位線(差分:BL/BLB)的列結構,當某一行被選中後(相當於選中了希望讀出的資料),該行儲存單元則會根據儲存的資料將位線對的某一條位線下拉,該訊號將被後續讀出電路讀出。如果把該行的儲存單元當成數位電路中的一個門(gate),則可以算出該門的扇出在100的數量級,遠遠偏離電路延遲(latency)的最優解數十倍。由於該門顯然處於關鍵路徑(criticalpath)上,可以想象,如果依靠儲存單元得到軌對軌輸出,不光對儲存器的讀出延遲的影響是災難性的,而且功耗也極大(E(peroperation)=VQ=CBLVDD2 )。有兩個思路可以改善這個問題:1. 仍然使用大訊號讀出(large-signal sensing),透過減小扇出,即減少單對位線上的儲存單元數量如使用多級(hierarchical BL)結構;2.使用小訊號讀出(small-signal sensing),即使用讀出放大器將位線的訊號放大,意味著不需要軌對軌的位線訊號即可讀出儲存單元的資料。我們這裡介紹第二個思路。因儲存器陣列的相似結構,讀出放大器不僅在SRAM中使用,在其他種類的儲存器如動態隨機儲存器(DRAM),快閃記憶體(Flash Memory)中也得到廣泛使用。從上面的簡介我們可以得到推出讀出放大器應該具有的特性:1.高速;2.面積小(SRAM可以有1000個以上的讀出放大器);3.低功耗。然而,我們知道FET的引數如閾值電壓在製造完成前可以看成隨機變數,無法控制。而在數量龐大的讀出放大器的客觀條件下,我們無法對單個讀出放大器的偏移電壓(offset voltage)做校準(calibration),這一點與鎖存型放大器在資料轉換器和高速有線通訊中的應用非常不同,因此我們必須使用結構簡單的低偏移讀出放大器。

歷史上多種放大器均被當做讀出放大器使用。對於模擬積體電路學習者最容易理解的讀出放大器則是靜態差分放大器。然而,這類放大器幾乎可以作為反面教材,具有靜態功耗大,無法將小訊號放大至軌對軌等缺點。將電流而非電壓作為輸入訊號的SRAM讀出放大器在2000年左右曾被研究,因其具有可以忽略輸入電容而幾乎沒有延遲的將儲存單元的驅動電流作為訊號放大的優點。然而,電流讀出放大器電路往往需要多級放大結構,太過複雜而導致面積太大的問題。經過長年的自然選擇,一類讀出放大器脫穎而出,它就是鎖存型讀出放大器。鎖存型讀出放大器具有幾乎所有的優點:高速,面積小/結構簡單,功耗低(無靜態功耗),軌對軌輸出。這裡介紹兩種經常被使用的鎖存型讀出放大器。

當然,需要指出的是,本文介紹的電路結構不僅僅只應用於讀出放大器,鎖存型讀出放大器的電路結構如StrongArm鎖存器的電路結構也在儲存器以外的領域作為比較器(comparator)、限幅器(limiter)、鎖存器(latch)被使用,這是由於它們和讀出放大器的功能相似性決定的。這些領域包括但不限於數模轉換電路、串並/並序列轉換器。

基於交叉耦合反相器(Cross-CoupledInverter)的讀出放大器

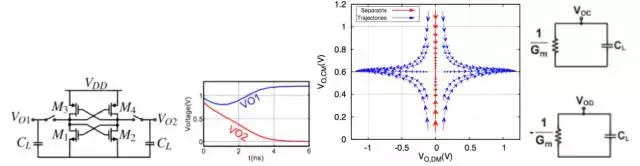

互動耦合方向器電路圖;電壓的時間演化和相空間圖;共模/差模等效電路;

對任何正反饋放大器的討論都應該從簡單且易於理解的互動耦合方向器開始。功耗:因為正反饋,放大器的輸入訊號將被放大至軌對軌。由於這個特性,在放大完成後,該電路的功耗降為零,這是鎖存型放大器普遍的特點。速度:對該電路有了定性的瞭解後,我們接著理解該正反饋電路的動力學過程。如果選取共模電壓和差模電壓作為獨立變數,我們可以透過基於基爾霍夫方程組的動力學方程組或基於模擬得到如圖所示的動力學相空間圖。從圖中我們可以明顯看出共模電壓和差模電壓是一對正交的變數,意味著兩者獨立變化而不受互相的影響。事實上我們可以得到其等效電路(如圖)。共模電壓對應的極點是穩定極點,而差模電壓對應的極點是不穩定極點,這兩個極點的位置由負載和反相器跨導決定。由於該電路的線性性直到差模電壓很大時才失效,因此極點的位置和輸入訊號的大小決定了該放大器的速度。偏移電壓:由於該放大器只有四個FET,根據pelgrom定律,在設計面積一定的情況下我們因此可以得到非常小的等效輸入偏移電壓。由於正反饋放大器的特點,我們不能使用對靜態放大器的分析方法分析該電路的偏移電壓公式,必須對該電路進行動力學分析,找出各個失配下的亞穩態(metastable point,數學上稱為“Saddle fixed point/鞍點不動點”)和對應的分界線(separatrix,圖中紅色直線,是失配的函式,數學上稱為“stable manifold/穩定流型”)。

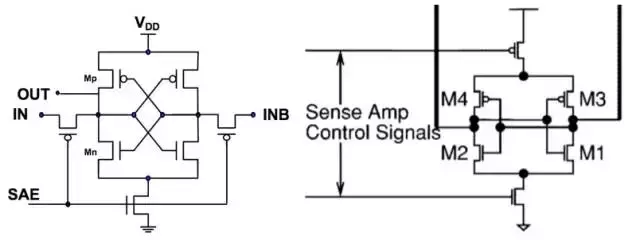

實際中基於互動耦合反相器的讀出放大器在其為核心的基礎上加上若干FET控制開關。該讀出放大器的一個重要特點是輸入節點和輸出節點相同。如在SRAM中,輸入共模電壓是VDD,使用最廣泛的讀出放大器則加上兩個FET用於隔離位線電容和一個用於開啟和關閉讀出放大器的FET,而無需在PFET端也加一個開關。有趣的是,利用正反饋特性,互動耦合反相同時也是SRAM 6T儲存單元的核心結構。在DRAM中,由於輸入共模電壓一般為VDD/2,因此需要兩個FET控制開啟關閉,並且由於DRAM需要重新寫入被讀出的儲存單元,因此不能隔離位線(大電容),這也是DRAM讀出一般比SRAM慢的一個重要原因。

SRAM/DRAM常用的讀出放大器;

StrongArm鎖存器

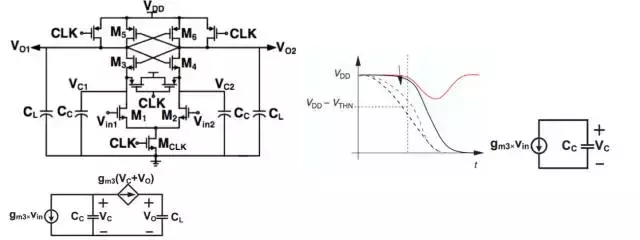

StrongArm電路圖;訊號隨時間演化(虛線:VC1/VC2;實線:VO1/VO2);差模小訊號等效電路:取樣;轉移;

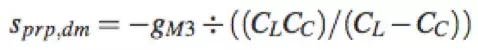

StrongArm鎖存器最初由Abidi教授的學生Kobayashi教授於1993年提出,得名於本電路在StrongArm微處理器中的使用。如圖所示,核心FET是M1-M6。這個電路提供了一個方便的方法,將輸入電壓耦合至互動耦合放大器,從而隔離了輸入和輸出埠:輸入電壓訊號透過輸入對管轉變成電流訊號,該電流訊號在輸出埠產生一個初始電壓使互動耦合放大器再生放大至軌對軌訊號,因而該電路在SRAM設計者中也被稱為電流鎖存讀出放大器。這個電路的動力學過程有三個階段:取樣,轉移,再生。每個階段伴隨著一定的訊號放大。初始時節點C和輸出節點O均為VDD。取樣階段時,所有互動耦合放大器的FET(M3-M6)均處於關斷,輸入訊號在電容CC上積分並在節點C形成一個訊號,同時伴隨著節點C的共模電壓下降。轉移階段時,M3和M4開啟並處於飽和區,差模小訊號等效電路如圖,該電路只有一個穩定極點:

同時注意到節點C和O的總電荷守恆,因此在此階段輸入訊號積分的所有電荷將被轉移至輸出節點並放大(穩定時VC為負),形成再生階段的初始電壓。再生階段的動力學行為則與互動耦合反向器非常相似。在瞭解了StrongArm鎖存器的原理以後,我們可以得到一個很顯然的結論:即為了保證再生階段的初始訊號足夠大(以抵抗FET失配),必須保證輸入對管始終處於飽和區(輸入共模電壓小於VDD-VTN),否則電荷將從輸入對管的等效電阻洩露從而訊號放大倍數大大降低。SRAM中使用的StrongArm鎖存器則存在這個問題,在固定面積的條件下,該讀出放大器的輸入偏移電壓約為之前介紹的讀出放大器的兩倍,這也是StrongArm鎖存器在SRAM應用中的主要缺點。然而,高速的StrongArm鎖存器則要求輸入共模電壓要大,從而將取樣和轉移階段的延遲降低,而基於互動耦合反相器的讀出放大器速度則與輸入共模電壓無關。

這裡需要指出,由於在儲存器應用中無法校準偏移電壓,因此噪聲是不重要的。在資料轉換器的應用中,則還要分析噪聲的貢獻。