[嵌入式]儲存器管理

儲存器管理

5.1 儲存器分類

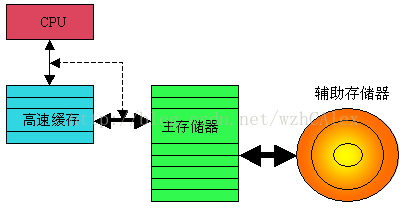

儲存器組織結構

在複雜的嵌入式系統中,儲存器系統的組織結構按作用可以劃分為4級:暫存器、cache、主儲存器和輔助儲存器,如下圖所示。當然,對於簡單的嵌入式系統來說,沒有必要把儲存器系統設計成4級,最簡單的只需暫存器和主儲存器即可。

儲存器作用示意圖

暫存器包含在微處理器內部,用於指令執行時的資料存放,如:R0,R15等。Cache是快取記憶體。主儲存器是程式執行程式碼及資料的存放區,通常採用SDRAM型別的儲存晶片。輔助儲存器通常是Flash型別的晶片,作用類似通用計算機中的外存。

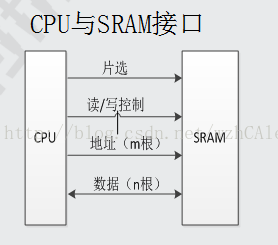

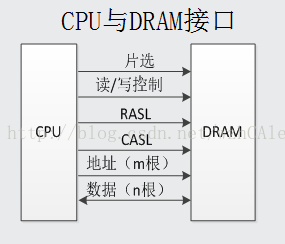

儲存單元識別

主儲存器和輔助儲存器內部的儲存單元靠地址來識別,儲存器晶片收到的n位地址訊號就選定一個具體的儲存單元。儲存器晶片通常還需一根使能訊號引腳,它控制著儲存器晶片資料引腳的三態。另外,還需讀/寫控制訊號引腳,它們控制著儲存器的資料傳送方向。

隨機儲存器和只讀儲存器

儲存器根據其存取方式分成兩類:隨機儲存器(RAM)和只讀儲存器(ROM)。RAM是易失性儲存器,ROM是非易失性儲存器。

隨機儲存器又分為兩大類:

·靜態隨機儲存器(SRAM)

·動態隨機儲存器(DRAM)

·SRAM讀/寫速度比DRAM快。

·SRAM比DRAM功耗大。

·DRAM整合度高,因而儲存容量更大。

·DRAM需要週期性的重新整理,而SRAM不需要。

SRAM中的儲存單元內容在通電狀態下是始終不會丟失的,因而,其儲存單元不需要定時重新整理。

DRAM中的儲存單元內容在通電狀態下會丟失,需要定期重新整理。因此增加RAS(行地址選擇)和CAS(列地址選擇)訊號線,這樣可以減少地址引腳,並方便重新整理操作。

只讀儲存器(ROM)

只讀儲存器(ROM)通常又分成EPROM、EEPROM和快閃記憶體(Flash)。目前,快閃記憶體作為只讀儲存器在嵌入式系統中被大量採用,快閃記憶體使用標準電壓既可擦寫和程式設計,因此,快閃記憶體在標準電壓的系統內就可進行程式設計寫入。

NOR和NAND是現在市場上兩種主要的非易失快閃記憶體技術。

NAND Flash和NOR Flash比較

·1988年,Intel首先開發出NOR Flash技術;

·1989年,東芝公司發表了NAND Flash結構的儲存器。

NAND Flash和NOR Flash比較,有以下特點:

·NOR Flash的讀取速度比NAND Flash稍快一些,NAND Flash的擦除和寫入速度比NOR Flash快很多。

·Flash晶片在寫入操作時,需要先進行擦除操作。NAND Flash的擦除單元更小,因此相應的擦除電路更少。

·NOR Flash帶有SRAM介面,有足夠的地址引腳來定址,可以很容易地存取其內部的每一個位元組,可以像其他SRAM儲存器那樣與微處理器連線;NAND Flash器件使用複雜的I/O口來序列地存取資料,各個產品或廠商的方法還各不相同,因此與微處理器的介面複雜。

·NAND Flash讀和寫操作採用512位元組的塊,這一點類似硬碟管理操作,很自然地,基於NAND Flash的儲存器就可以取代硬碟或其他塊裝置。

5.2 記憶體管理單元

MMU,全稱Memory Manage Unit, 中文名—儲存器管理單元。

許多年以前,當人們還在使用DOS或是更古老的作業系統的時候,計算機的記憶體還非常小,一般都是以K為單位進行計算,相應的,當時的程式規模也不大,所以記憶體容量雖然小,但還是可以容納當時的程式。但隨著圖形介面的興起還用使用者需求的不斷增大,應用程式的規模也隨之膨脹起來,終於一個難題出現在程式設計師的面前,那就是應用程式太大以至於記憶體容納不下該程式。

虛擬記憶體

虛擬記憶體的基本思想是程式,資料,堆疊的總的大小可以超過物理儲存器的大小,作業系統把當前使用的部分保留在記憶體中,而把其他未被使用的部分儲存在磁碟上。比如對一個16MB的程式和一個記憶體只有4MB的機器,OS通過選擇,可以決定各個時刻將哪4M的內容保留在記憶體中,並在需要時在記憶體和磁碟間交換程式片段,這樣就可以把這個16M的程式執行在一個只具有4M記憶體機器上了。而這個16M的程式在執行前不必由程式設計師進行分割。

虛擬地址

任何時候,計算機上都存在一個程式能夠產生的地址集合,我們稱之為地址範圍。這個範圍的大小由CPU的位數決定,例如一個32位的CPU,它的地址範圍是0~0xFFFFFFFF (4G),而對於一個64位的CPU,它的地址範圍為0~0xFFFFFFFFFFFFFFFF (64T)。這個範圍就是我們的程式能夠產生的地址範圍,我們把這個地址範圍稱為虛擬地址空間,該空間中的某一個地址我們稱之為虛擬地址。

實體地址

與虛擬地址空間和虛擬地址相對應的則是實體地址空間和實體地址,大多數時候我們的系統所具備的實體地址空間只是虛擬地址空間的一個子集,這裡舉一個最簡單的例子直觀地說明這兩者,對於一臺記憶體為256MB的32bit x86主機來說,它的虛擬地址空間範圍是0~0xFFFFFFFF(4G),而實體地址空間範圍是0x000000000~0x0FFFFFFF(256MB)。

地址對映

在沒有使用虛擬儲存器的機器上,虛擬地址被直接送到記憶體匯流排上,使具有相同地址的物理儲存器被讀寫。而在使用了虛擬儲存器的情況下,虛擬地址不是被直接送到記憶體地址匯流排上,而是送到記憶體管理單元——MMU,其功能是把虛擬地址對映為實體地址。

大多數使用虛擬儲存器的系統都使用一種分頁技術。虛擬地址空間劃分成稱為頁(page)單位,而相應的實體地址空間也被進行劃分,單位是頁框(frame)。頁和頁框的大小必須相同。

這個例子有一臺可以生成16位地址的機器,虛擬地址範圍0x0000~0xFFFF(64K),而這臺機器只有32K的實體地址,他可以執行64K的程式,但該程式不能一次性調入記憶體執行。

例如,當一條指令將將0號地址的值傳遞進暫存器REG,核心執行的過程如下:

首先,虛擬地址0將被送往MMU,MMU看到該虛地址落在頁0範圍內(頁0範圍是0到4095),從上圖我們看到頁0所對應(對映)的頁框為2(頁框2的地址範圍是8192到12287),因此MMU將該虛擬地址轉化為實體地址8192,並把地址8192送到地址匯流排上。記憶體對MMU的對映一無所知,它只看到一個對地址8192的讀請求並執行它。MMU從而把0到4096的虛擬地址對映到8192到12287的實體地址。

系統上電前,所有的程式和資料都儲存在FLASH中。系統上電後,異常中斷處理和資料棧就被移到32位的RAM中,使異常中斷處理速度較快;RW資料以及ZI資料移到16位RAM中;其他的RO程式碼在FLASH中執行。系統復位時,FLASH位於地址0處,復位後開始執行的指令把FLASH對映到別的非0地址段,而把RAM對映到地址0處。

系統初始化

系統初始化有兩個階段:

1. 初始化執行環境

——設定入口地址

——設定異常向量表和中斷向量表

——初始化儲存器系統

——初始化堆疊

——初始化關鍵的I/O裝置

——初始化中斷系統需要的RAM變數

——中斷使能

——切換處理器模式和處理器狀態

2. 初始化應用程式

——初始化非0可寫變數

——對ZI資料段清0

——對有作業系統的應用系統,執行環境在作業系統啟動時初始化,然後通過main()

函式自動進入應用程式,C執行時庫中的_main()函式初始化應用程式。對於沒有操

作系統的應用系統,ROM中的程式碼必須提供—種應用程式初始化自身和開始執行

的方法。

5.3 S5PV210的儲存系統

儲存系統框圖

TLB及TTW

MMU本身有少量儲存空間存放從虛擬地址到實體地址的匹配表,此表稱作TLB(快表,也稱頁表)。TLB中內容包括:虛址及其對應的實體地址,許可權,域和對映型別。

當CPU對一虛擬地址進行存取時首先搜尋TLB表以查詢對應的實體地址等資訊,稱為Translation Table Walk,TTW。經過TTW過程後,將查到的資訊儲存到TLB,然後根據TLB表項的實體地址進行讀寫

S5PV210儲存器地址對映

S5PV210啟動過程

S5PV210上電將從IROM處執行固化的啟動程式碼BL0,它對時鐘等初始化、對啟動裝置進行判斷,並從啟動裝置中複製BL1(最大16KB)到IRAM地址0xd0020000處,其中0xd0020010之前的16個位元組儲存的BL1的校驗資訊和BL1尺寸,對BL1進行校驗,校驗成功後轉入BL1進行執行。

BL0:IROM中固化啟動程式碼;

BL1:在IRAM自動從外儲存器(nand/sd/usb)中拷貝的uboot.bin二進位制檔案頭16K程式碼;

BL2:在程式碼重定向後在記憶體中執行的UBOOT完整程式碼。

5.4 S5PV210的記憶體控制器

DRAM控制器

DRAM控制器是高階微控制匯流排結構(AMBA)AXI。為支援高速儲存裝置,DRAM控制器使用SEC DDR PHY介面。S5PV210有兩個獨立的DRAM控制器和介面DMC0和DMC1。DMC0和DMC1支援的最大記憶體容量分別為512M位元和1G位元,但這兩個控制器必須使用同樣記憶體容量。其主要特性有:

·相容JEDEC DDR2、低功率DDR和、DDR2 SDRAM標準;

·使用SEC LPDDR2 PHY介面來支援高速儲存裝置;

·支援兩個外部晶片選擇和每晶片包含1/2/4/8個儲存體;

·支援128 MB, 256 MB, 512 MB, 1 GB, 2 GB and 4 GB的密度儲存裝置;

·支援16/32位元的儲存資料頻寬。

SROM控制器

S5PV210 SROM支援外接8/16位元NOR Flash/PROM/SRAM儲存器。共支援6個高達16MB的儲存體。

SROM控制器的主要特性有:

· 支援SRAM,各種ROM和NOR快閃記憶體;

· 僅支援8位元或16位元的資料匯流排;

· 地址空間:每儲存體可達16MB;

· 支援6個儲存體;

· 記憶體的起始地址固定;

· 支援位元和半字。

OneNand控制器

S5PV210支援用於OneNAND和Flex-OneNAND儲存裝置的外部匯流排。該OneNAND控制器支援非同步和同步匯流排讀寫操作,該控制器還整合專用DMA引擎對儲存裝置操作進行加速。

OneNand控制器的主要特性有:

·支援資料緩衝(23位預讀取FIFO和32位輸出FIFO)。

·為匹配OneNAND和AHB系統匯流排介面速度,支援非同步FIFO。

·支援OneNAND快閃記憶體裝置的同步和非同步讀/寫。

·可程式設計突發傳輸大小的OneNAND快閃記憶體介面。

·支援16位資料通道記憶體和32位資料通道AHB系統匯流排介面。

·用單一匯流排介面協議支援OneNAND家族多種儲存裝置。

·最多支援兩個OneNAND裝置。

·支援OneNAND裝置的復位功能。

NAND 快閃記憶體控制器

S5PV210上的啟動程式可以在外部NAND快閃記憶體中執行。它會將NAND快閃記憶體上的資料拷貝到DRAM中。當NAND快閃記憶體內容被複制到DRAM之後,主程式會在DRAM上執行。

NAND控制器的主要特性有:

·NAND快閃記憶體介面:支援512位元組,2KB,4KB,8KB頁面。

·軟體模式可以直接訪問NAND快閃記憶體,例如用於讀/擦除/程式設計NAND快閃記憶體。

·支援8位NAND快閃記憶體介面匯流排。

·支援SLC和MLC NAND快閃記憶體。

·支援1 /4 /8/12 /16位ECC。

·支援位元組/半字/字資料。

NAND Flash讀寫擦除程式

1.初始化函式 Nand_init():

void Nand_Init(void)

{rNFCONF = 0x7771;

rNFCONT = 0x03 ;

}

2. NAND Flash復位函式

static void Nand_Reset(void)

{ NF_nFCE_L();/* select this chip */

NF_CLEAR_RB(); /* clear the r/b bits*/

NF_CMD(CMD_RESET); /* reset cmd*/

NF_DETECT_RB();/* detect the bit status*/

NF_nFCE_H();/* disa the chip*/

}

3.寫頁面資料

static int nand_write_page(unsigned char *buf, unsigned long addr)

{

unsigned char *ptr = (unsigned char *)buf;

unsigned int i;

NF_nFCE_L(); NF_CLEAR_RB();

NF_CMD(0x80); addr = addr >> 11;

NF_ADDR(0); NF_ADDR(0);

NF_ADDR(addr& 0xff);

NF_ADDR((addr>>8) & 0xff);

NF_ADDR((addr>>16) & 0xff);

for (i = 0; i < (2048); i++)

{ rNFDATA8 = *ptr; ptr++; }

NF_CMD(0x10); NF_DETECT_RB();

NF_CMD(0x70); NF_WAITIO0();

NF_nFCE_H();

return 2048;

}

4. 擦除塊資料

static int nand_erase_block(unsigned long addr)

{ NF_nFCE_L() ;//chip Enable

NF_CLEAR_RB();

NF_CMD(CMD_ERA1);

addr= addr>>11;

NF_ADDR(addr & 0xff);

NF_ADDR((addr>>8) & 0xff);

NF_ADDR((addr>>16) & 0xff);

NF_CMD(CMD_ERA2);

NF_DETECT_RB()

NF_CMD(0x70);

NF_WAITIO0();

/* chip Disable */

NF_nFCE_H();

return 0;

}

5.讀函式

static int nand_read_page(unsigned long addr, unsigned char * const buffer)

{

int i;

addr = addr>>11;

//Nand_Reset();

NF_nFCE_L();

NF_CLEAR_RB();

NF_CMD(CMD_READ1);

NF_ADDR(0x0);

NF_ADDR(0x0);

NF_ADDR(addr&0xff);

NF_ADDR((addr>>8)&0xff);

NF_ADDR((addr>>16)&0xff);

NF_CMD(CMD_READ2);

//delay(500);

NF_DETECT_RB();

for (i = 0; i < 2048; i++)

{

buffer[i] = NF_RDDATA8();

}

NF_nFCE_H();

return 0;

}

相關文章

- 嵌入式中常見的儲存器總結(一)儲存器分類

- 新興儲存器鐵電RAM嵌入式應用

- 儲存管理

- 儲存器

- Ceph儲存池管理

- 主儲存器

- 外部儲存器

- 傳統儲存器和新興儲存器應用

- 003.DirectPV儲存管理

- docker儲存配置與管理Docker

- 儲存系列1-openfiler開源儲存管理平臺實踐

- 儲存器的知識

- 只讀儲存器ROM

- 高速率儲存器UFS

- 20932虛擬儲存器

- 儲存、檔案管理/目錄、裝置管理

- 塊儲存 檔案儲存 物件儲存物件

- SRAM是什麼儲存器

- Flash儲存器的故障特徵特徵

- 常見儲存器分類

- 瀏覽器儲存的方法瀏覽器

- 資料儲存(1):從資料儲存看人類文明-資料儲存器發展歷程

- 儲存—物件儲存_Minio物件

- Lerna --多包儲存管理工具

- 分割槽儲存管理模擬實驗

- 理解作業系統之儲存管理作業系統

- 華為雲學院乾貨:物件儲存服務:便捷管理儲存資源物件

- 如何延長儲存伺服器上資料的儲存時間?伺服器

- 行式儲存 列式儲存

- 雲原生儲存編排器Rook

- 伺服器資料的儲存伺服器

- 【計組】3.7 虛擬儲存器

- 第5章 虛擬儲存器

- 非易失性儲存器EEPROM

- 儲存器的層次結構

- linux6-儲存結構與硬碟管理Linux硬碟

- 阿里雲OSS雲端儲存管理實踐阿里

- CynosDB技術詳解——儲存叢集管理

- 阿里雲物件儲存OSS支援版本管理特性阿里物件