AHB匯流排協議

1. 簡介

AHB匯流排規範是AMBA匯流排規範的一部分,AMBA匯流排規範是ARM公司提出的匯流排規範,被大多數SoC設計採用,它規定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用於高效能、高時脈頻率的系統結構,典型的應用如ARM核與系統內部的高速RAM、NAND FLASH、DMA、Bridge的連線。APB用於連線外部裝置,對效能要求不高,而考慮低功耗問題。ASB是AHB的一種替代方案。1.1 AHB匯流排的架構

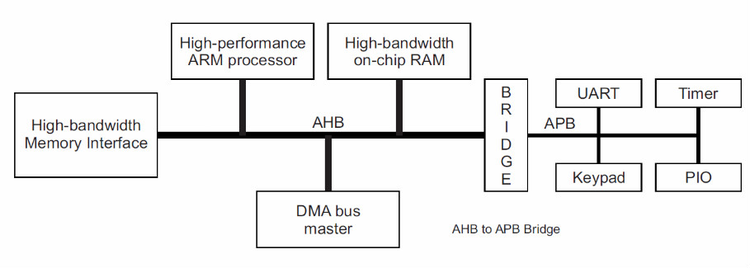

AHB匯流排的強大之處在於它可以將微控制器(CPU)、高頻寬的片上RAM、高頻寬的外部儲存器介面、DMA匯流排master、各種擁有AHB介面的控制器等等連線起來構成一個獨立的完整的SOC系統,不僅如此,還可以通過AHB-APB橋來連線APB匯流排系統。AHB可以成為一個完整獨立的SOC晶片的骨架。下圖是一個典型的AHB系統匯流排的結構示意圖

1.2 AHB基本特性

- Burst傳輸

- Split事務處理

- 單週期master移交

- 單一時鐘沿操作

- 無三態

- 更寬的資料匯流排配置(64/128)

- 流水線操作

- 可支援多個匯流排主裝置(最多16個)

2. AHB匯流排的組成

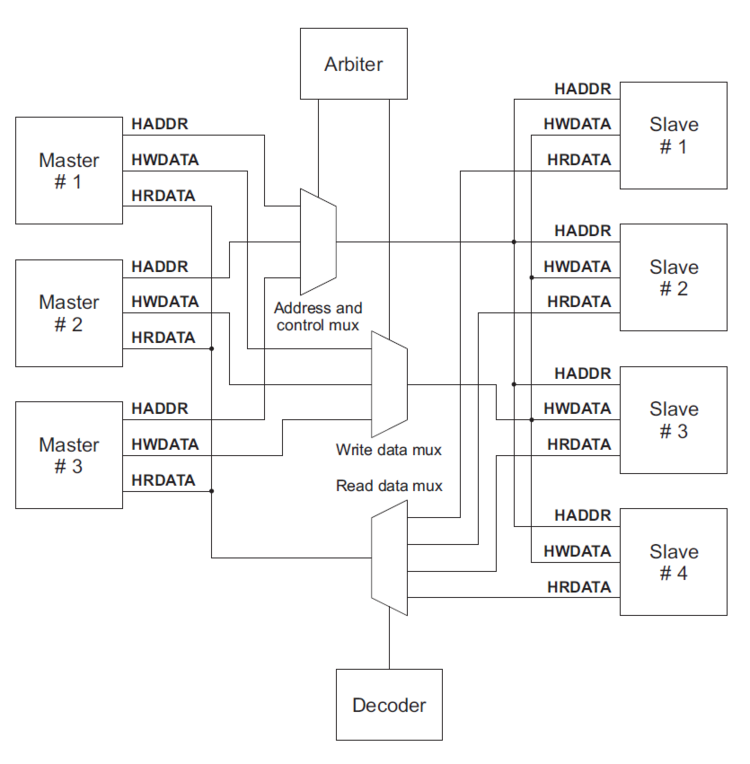

AHB匯流排由Master、Slave和Infrastructure構成。Infrastructure由arbiter、資料多路、地址控制多路、譯碼器構成。

某一時刻只允許一個主裝置使用匯流排

通過地址對映來選擇使用哪一個從裝置

讀資料匯流排(HRDATA)

地址控制匯流排(HADDR)

- 主裝置Master

某一時刻只允許一個主裝置使用匯流排

- 從裝置Slave

通過地址對映來選擇使用哪一個從裝置

- 仲裁器arbiter

- 譯碼器decoder

- 匯流排可以分為三組

讀資料匯流排(HRDATA)

地址控制匯流排(HADDR)

3. 訊號描述

| Name | Source | To | Description |

| HCLK | clock source | 各module | 匯流排時鐘,上升沿取樣 |

| HRESETn | reset controller | 各module | 匯流排復位,低電平有效 |

| HADDR[31:0] | Master | decoder mux to slave arbiter |

32位系統地址匯流排 |

| HTRANS[1:0] | Master | mux to slave | 當前傳輸型別NONSEQ, SEQ, IDLE, BUSY |

| HWRITE | Master | mux to slave | 1為寫,0為讀 |

| HSIZE[2:0] | Master | mux to slave | 每一個transfer傳輸的資料大小,以位元組為單位,最高支援1024位 |

| HBURST[2:0] | Master | mux to slave | burst型別,支援4、8、16 burst,incrementing/wrapping |

| HPROT[3:0] | Master | mux to slave | 保護控制訊號,需要slave帶保護功能,一般不用 |

| HWDATA[31:0] | Master | mux to slave | 寫資料匯流排,Master到Slave |

| HRDATA[31:0] | Slave | mux to master | 讀資料匯流排,Slave到Master |

| HREADY | Slave | mux to master arbiter |

高:Slave指出傳輸結束 低:Slave需延長傳輸週期 |

| HRESP[1:0] | Slave | mux to master arbiter |

Slave發給Master的匯流排傳輸狀態OKAY, ERROR, RETRY, SPLIT |

| HSELx | Decoder | slave | slave選擇訊號 |

AHB仲裁訊號

| Name | Source | To | Description |

| HBUSREQx | Master | arbiter | master給仲裁器的請求獲得匯流排使用權的請求訊號,最多支援16個master |

| HLOCKx | Master | arbiter | 如果一個master希望自己在傳輸期間不希望丟掉匯流排,則需要向仲裁器傳送這個鎖定訊號 |

| HGRANTx | arbiter | master | 授權訊號,當前bus master x的優先順序最高。當HREADY和HGRANTx同時為高時,master獲取系統匯流排的權利 |

| HMASTER [3:0] | arbiter | 具有split功能的slave | 仲裁器為每一個master分配的ID,指出哪個主裝置正在進行傳輸,提供進行split的資訊 |

| HMASTLOCK | arbiter | 具有split功能的slave | 表示當前的master正在執行Locked操作。這個訊號和HMASTER有這相同的時序 |

| HSPLITx[15:0] | slave | arbiter | 從裝置用這個訊號告訴仲裁器哪個主裝置執行重新嘗試一次split傳輸,每一位對應一個主裝置 |

4. 匯流排操作

有需要佔用匯流排的Master向arbiter發出請求,arbiter授權給指定的master。任一時間週期只有一個master可以接入匯流排,對其指定的slave進行讀寫操作。獲得授權的匯流排開始AHB傳輸,首先發出地址和控制訊號,提供地址資訊、傳輸方向、頻寬和burst型別。匯流排統一規劃slave的地址,譯碼器根據地址和控制訊號確定哪個slave與master進行資料通訊。資料傳輸通過資料匯流排完成。為避免出現三態匯流排,AHB將讀寫匯流排分開,寫資料匯流排用於從master到slave的資料傳輸,讀資料匯流排用於從slave到master的資料傳輸。每筆傳輸包括一個地址和控制週期,一個或多個資料週期。地址和控制週期不能被擴充套件,因此slave必須在一個週期內取樣地址訊號。資料週期可以通過HREADY訊號擴充套件,但HREADY為低時給傳輸加入一個等待狀態以使slave獲得額外的時間來提供或取樣資料,另外slave通過響應訊號HRESP反映傳輸狀態。

一般情況下master完成完整的burst傳輸,arbiter才會授權給其他的master接入匯流排,然而為避免過大的判決延遲,arbiter也可能打斷burst傳輸。在這種情況下master必須再次接入匯流排以進行中斷的burst剩餘部分的傳輸。

5. 基本傳輸

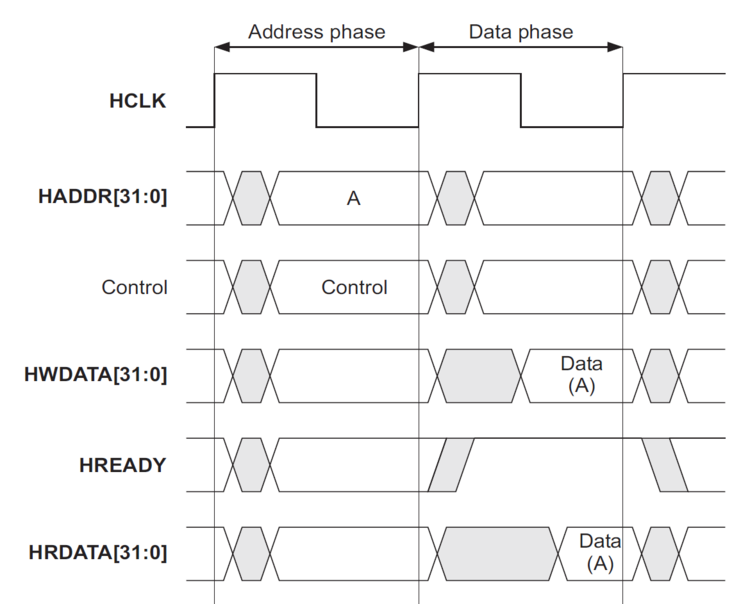

一筆傳輸由如下兩部分組成:地址階段:一個週期

資料階段:一個或多個週期,由HBURST訊號決定需要幾個有效週期,可以由HREADY發出請求延長一個週期。

5.1 沒有等待狀態的single transfer

第一個週期的上升沿,master驅動地址和控制訊號;

第二個週期的上升沿,slave取樣地址和控制訊號,並將HREADY拉高;

如果是寫操作,master會在第二個週期的上升沿傳輸要寫入的資料;

如果是讀操作,slave會在HREADY訊號拉高後將讀取的資料寫入匯流排;

第三個週期的上升沿,

如果是寫操作,master獲取HREADY高訊號,表明slave已成功接收資料,操作成功;

如果是讀操作,master獲取HREADY高訊號,表明此時的讀資料有效並且接收下來,操作成功。

需要注意,HREADY訊號在資料有效期間必須為高,並且延續到第三個週期的上升沿之後,確保master的正確取樣。

第二個週期的上升沿,slave取樣地址和控制訊號,並將HREADY拉高;

如果是寫操作,master會在第二個週期的上升沿傳輸要寫入的資料;

如果是讀操作,slave會在HREADY訊號拉高後將讀取的資料寫入匯流排;

第三個週期的上升沿,

如果是寫操作,master獲取HREADY高訊號,表明slave已成功接收資料,操作成功;

如果是讀操作,master獲取HREADY高訊號,表明此時的讀資料有效並且接收下來,操作成功。

需要注意,HREADY訊號在資料有效期間必須為高,並且延續到第三個週期的上升沿之後,確保master的正確取樣。

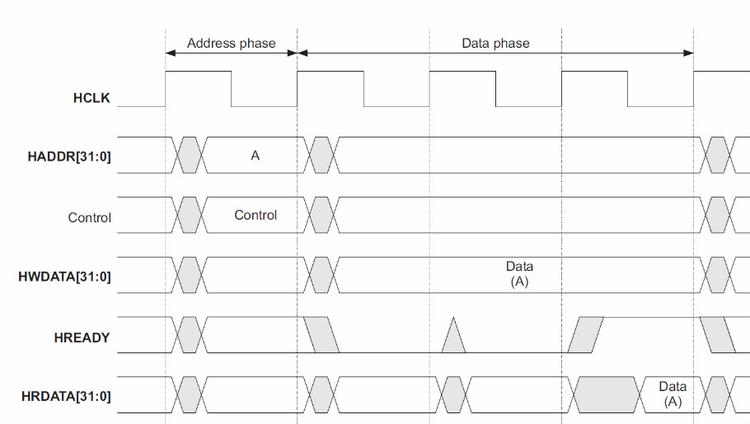

5.2 slave插入等待狀態的single transfer

slave可以及時處理master請求,但也可能存在slave太慢不能立即處理的情況。這時需要讓master稍微等一等,需要slave插入一些等待的狀態。如下圖所示,HREADY訊號在第二和第三週期拉低,意在告訴master,slave不能立即處理,需要master等待2個週期。在這裡需要注意2點:

如果是寫操作,master需要在等待期間保持寫資料不變,直到本次傳輸完成;

如果是讀操作,slave不需要一開始就給出資料,僅當HREADY拉高後才給出有效資料。

如果是寫操作,master需要在等待期間保持寫資料不變,直到本次傳輸完成;

如果是讀操作,slave不需要一開始就給出資料,僅當HREADY拉高後才給出有效資料。

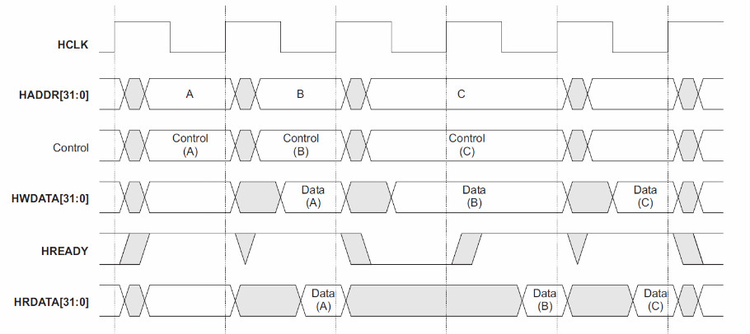

5.3 多個single transfer的pipeline操作

擴充套件資料週期的一個負效應是必需延長相應的下一筆傳輸的地址週期。A和C為零等待傳輸,B加入了一個等待週期,因此相應的C地址週期要進行擴充套件。

第一個週期,master發起一個操作A,並驅動地址和控制訊號;

第二個週期,slave收到了來自匯流排的請求,將HREADY訊號拉高;

第二個週期上升沿後,master發現有操作B需要執行,並且檢查到上一週期的HREADY為高,則發起第二個操作B;

第三個週期,master獲取HREADY訊號為高,表示操作A已經完成;

第三個週期上升沿後,master發現有操作C需要執行,並且檢查到上一週期的HREADY為高,則發起第三個操作C;

第三個週期上升沿後,slave由於繁忙插入了一個等待狀態,將HREADY拉低;

第四個週期,master獲取HREADY訊號為低,知道slave希望等待,於是master保持和上一拍一樣的訊號;

第四個週期,slave處理完了事務,將HREADY訊號拉高,表示可以繼續處理;

第五個週期,master獲取HREADY訊號為高,知道slave已經可以處理B操作;

第五個週期上升沿後,B操作完成;

第六個週期上升沿後,C操作完成。

需要注意幾點:

HREADY在一定程度上表示了slave的pipeline能力,在AHB中是2個pipe,也就是匯流排上最多存在2個未處理完的transfer。只有當匯流排上未完成的transfer少於2個時,master才能發起操作。

第一個週期,master發起一個操作A,並驅動地址和控制訊號;

第二個週期,slave收到了來自匯流排的請求,將HREADY訊號拉高;

第二個週期上升沿後,master發現有操作B需要執行,並且檢查到上一週期的HREADY為高,則發起第二個操作B;

第三個週期,master獲取HREADY訊號為高,表示操作A已經完成;

第三個週期上升沿後,master發現有操作C需要執行,並且檢查到上一週期的HREADY為高,則發起第三個操作C;

第三個週期上升沿後,slave由於繁忙插入了一個等待狀態,將HREADY拉低;

第四個週期,master獲取HREADY訊號為低,知道slave希望等待,於是master保持和上一拍一樣的訊號;

第四個週期,slave處理完了事務,將HREADY訊號拉高,表示可以繼續處理;

第五個週期,master獲取HREADY訊號為高,知道slave已經可以處理B操作;

第五個週期上升沿後,B操作完成;

第六個週期上升沿後,C操作完成。

需要注意幾點:

HREADY在一定程度上表示了slave的pipeline能力,在AHB中是2個pipe,也就是匯流排上最多存在2個未處理完的transfer。只有當匯流排上未完成的transfer少於2個時,master才能發起操作。

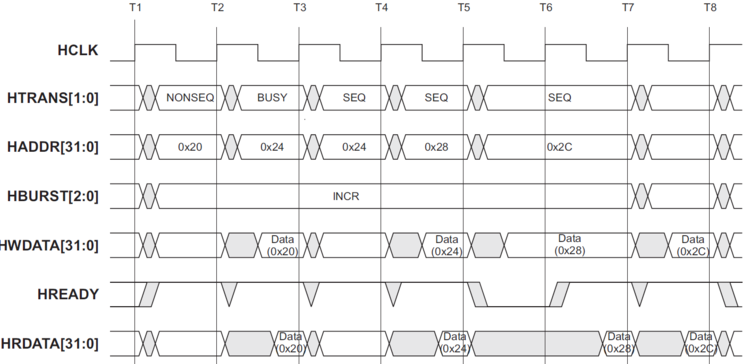

5.4 遞增burst

T1,master傳入地址和控制訊號,因為是新的burst開始,transfer的型別是NONSEQ;

T2,由於master不能在第二個週期裡處理第二拍,所以master使用BUSY transfer來為自己延長一個週期的時間。注意,雖然是延長了一個週期,但是master需要給出第二個transfer的地址和控制訊號;

T3,slave採集到了master發來的BUSY,知道master需要等待一拍,所以slave會忽略這個BUSY transfer;

T3,master發起了第二個transfer,因為是同一個burst的第二個transfer,所以transfer的型別是SEQ;

T5,slave將HREADY訊號拉低,告訴master需要等待一個週期;

T8時刻完成最後一個transfer。

需要注意的 雖然slave會忽略掉BUSY transfer,但是master也需要給出下一拍的地址和控制訊號。

T2,由於master不能在第二個週期裡處理第二拍,所以master使用BUSY transfer來為自己延長一個週期的時間。注意,雖然是延長了一個週期,但是master需要給出第二個transfer的地址和控制訊號;

T3,slave採集到了master發來的BUSY,知道master需要等待一拍,所以slave會忽略這個BUSY transfer;

T3,master發起了第二個transfer,因為是同一個burst的第二個transfer,所以transfer的型別是SEQ;

T5,slave將HREADY訊號拉低,告訴master需要等待一個週期;

T8時刻完成最後一個transfer。

需要注意的 雖然slave會忽略掉BUSY transfer,但是master也需要給出下一拍的地址和控制訊號。

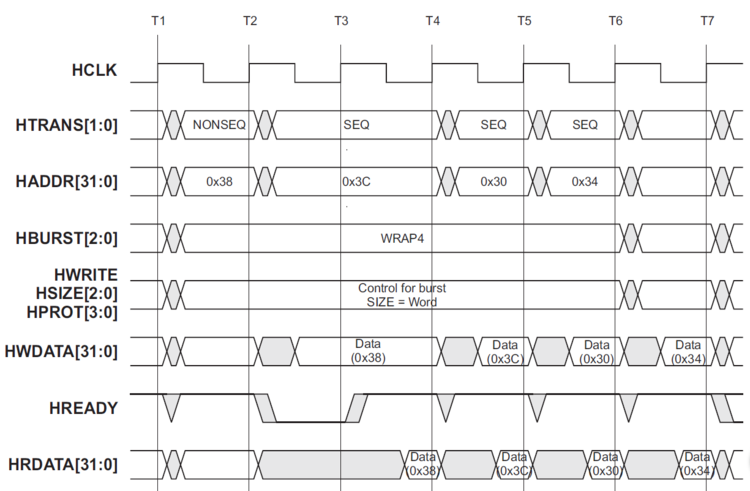

5.5 wrapping 4-beat burst

跟之前唯一的區別在於地址的不同,在0x3C地址之後,根據迴環的地址邊界,第三拍的地址變為0x30。一共四拍,4個地址,每個地址各不相同,這四個地址是一個迴環範圍。起始地址決定了迴環操作的迴環範圍。

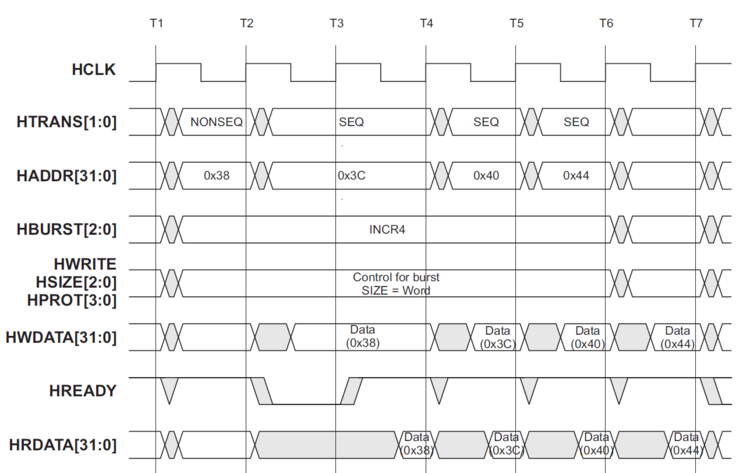

5.6 遞增4拍burst

和上面的基本一致,只不過地址在0x30並不迴環,而是遞增。

6.控制訊號

| HTRANS[1:0] |

傳輸型別 |

Description |

| 00 | IDLE | 主裝置佔用匯流排,但沒進行傳輸 兩次burst傳輸中間主裝置可發IDLE 此時就算slave被使能,也不會從匯流排上獲取任何的資料訊號。如果此時salve被選中,那麼每一個IDLE週期slave都要通過HRESP[1:0]返回一個OKAY響應 |

| 01 | BUSY | 主裝置佔用匯流排,但是在burst傳輸過程中還沒有準備好進行下一次傳輸 一次burst傳輸中間主裝置可發BUSY 這時slave不會從匯流排上收取資料而是等待,並且通過HRESP[1:0]返回一個OKAY響應。需要注意的是,這個transfer需要給出下一拍的地址和控制訊號,儘管slave不會去取樣。 |

| 10 | NONSEQ | 表明一次單個資料的傳輸或者一次burst傳輸的第一個資料 地址和控制訊號與上一次傳輸無關 |

| 11 | SEQ | burst傳輸接下來的資料 地址和上一次傳輸的地址是相關的,這時匯流排上的控制訊號應當與之前的保持一致,地址視情況遞增或者回環。 |

| HSIZE[2:0] | Size | Description |

| 000 | 8 bits | Byte |

| 001 | 16 bits | Halfword |

| 010 | 32 bits | Word |

| 011 | 64 bits | - |

| 100 | 128 bits | 4-word line |

| 101 | 256 bits | 8-word line |

| 110 | 512 bits | - |

| 111 | 1024 bits | - |

- Burst傳輸型別

| HBURST[2:0] | 型別 | Description |

| 000 | SINGLE | Single transfer |

| 001 | INCR | Incrementing burst of unspecified length |

| 010 | WRAP4 | 4-beat wrapping burst |

| 011 | INCR4 | 4-beat increment burst |

| 100 | WRAP8 | 8-beat wrapping burst |

| 101 | INCR8 | 8-beat increment burst |

| 110 | WRAP16 | 16-beat wrapping burst |

| 111 | INCR16 | 16-beat increment burst |

- 響應訊號

slave可以如下方式完成一筆傳輸:

- 立即完成一筆傳輸;

- 延遲一個或幾個週期完成傳輸;

- 傳輸失敗返回error;

- 延遲傳輸,釋放匯流排。

- 傳輸完成HREADY

傳輸響應HRESP[1:0]

00: OKAY

01: ERROR

10: RETRY

傳輸未完成,請求主裝置重新開始一個傳輸,arbiter會繼續使用通常的優先順序

11: SPLIT

傳輸未完成,請求主裝置分離一次傳輸,arbiter會調整優先順序方案以便其他請求匯流排的主裝置可以訪問匯流排

- 地址譯碼

每個slave最小的地址空間為1KB,所有的master的burst傳輸上限也是1KB,如此設計保證了不會出現地址越界問題。當一個設計不會用到所有的地址空間時,可能出現訪問到一個不存在的地址的情況,這就需要增加一個附加的預設slave來為上面的情況提供一個響應。當SEQ或NONSEQ傳輸訪問到一個不存在的地址,預設slave應該提供ERROR響應;當IDLE或BUSY傳輸訪問到一個不存在的地址,預設slave會響應OKAY。地址譯碼器會帶有實現預設slave的功能。

- 仲裁

HBUSREQx:master向arbiter發出接入請求的訊號。

HLOCKx:指示是否要進行不可中斷的傳輸,這一訊號與HBUSREQx同時由master向arbiter發出。

HGRANTx:arbiter產生指示master獲得授權,當HGRANTx訊號為高同時HREADY為高時,master可以向匯流排傳輸地址訊號。

HMASTER[3:0]:arbiter產生指示哪個master獲得授權,這一訊號用於地址控制多路來選擇哪個master接入匯流排。

HMASTERLOCK:arbiter產生指示當前傳輸是否為鎖定序列傳輸。

HSPLIT:供支援SPLIT傳輸使用。

相關文章

- ARM 匯流排協議協議

- 匯流排協議系列——USART協議初探協議

- CAN匯流排協議 學習筆記協議筆記

- 學習筆記-Verilog實現IIC匯流排協議筆記協議

- CAN匯流排分析儀工具-CAN轉USB智慧協議轉換器協議

- CAN匯流排協議簡介及其常見的應用領域協議

- 匯流排

- 事件匯流排事件

- 原創單匯流排傳輸協議b2s (附全部verilog原始碼)協議原始碼

- 6.匯流排

- I2C匯流排 | I2C匯流排介紹

- 將Abp預設事件匯流排改造為分散式事件匯流排事件分散式

- Can匯流排介紹

- Vue 事件中央匯流排Vue事件

- Vue事件匯流排(EventBus)Vue事件

- PCI匯流排基本概念

- 序列匯流排的學習

- CAN匯流排原理_學習

- I2C 匯流排

- 計算匯流排頻寬

- 大資料匯流排(DataHub)大資料

- Volatile如何保證執行緒可見性之匯流排鎖、快取一致性協議執行緒快取協議

- 企業服務匯流排ESB

- Flutter中的事件匯流排(EventBus)Flutter事件

- SpringCloud(六)Bus訊息匯流排SpringGCCloud

- SOFA 原始碼分析— 事件匯流排原始碼事件

- 手寫訊息匯流排LiveDataBusLiveData

- LLM-kimi:BMS-CAN匯流排

- MACH SYSTEMS—匯流排介面轉換工具Mac

- CAN匯流排取樣點測試

- 自己動手寫事件匯流排(EventBus)事件

- SAE J1850 汽車匯流排協議 VPW 物理層驅動程式在STM32晶片上的實現協議晶片

- 事件匯流排的設計與實現事件

- Spring Cloud Bus 訊息匯流排介紹SpringCloud

- 比 EventBus 更高效的事件匯流排(BusUtils)事件

- EventBridge 事件匯流排及 EDA 架構解析事件架構

- Flutter基礎-036-事件匯流排EventBusFlutter事件

- 事件匯流排EventBus和觀察者模式事件模式

- Android元件化之(路由 vs 元件匯流排)Android元件化路由