相信所有和計算機體系結構打過交道的朋友們都看過David Patterson與John Hennessy的煌煌鉅作,《計算機體系架構:量化研究方法》。兩位在計算機架構領域鼎鼎大名的教授,一個來自加州大學伯克利分校,另一個來自史丹佛。

《計算機體系架構:量化研究方法》自1990年第一版出版後,如今已經過了近30年,2011年第五版出版,目前Patterson和Hennessy正在準備第六版的書稿。計算機處理器領域滄海桑田,1990年時處理器是最熱門,最前沿的科技,是無數年輕人最神往的方向,摩爾定律推動晶片時脈頻率蒸蒸日上,未來一片大好。到了今天,處理器的技術含量仍然是所有科技裡面最高的之一,但是早已不是最熱門的科技,Intel擠牙膏式的工藝演進計劃預示著摩爾定律的終結似乎就在明天,處理器的未來如何人們眾說紛紜。Hennessy從史丹佛校長的位置上退了下來,Patterson也從伯克利退休。兩位巨星級的人物在三月份再次在史丹佛聚首,為我們帶來了一次精彩的演講。矽說的作者有幸在現場聆聽了這次演講,記錄如下。

首先上場的是David Patterson,為我們帶來了關於指令集架構(ISA)的回顧以及RISC-V專案的展望。

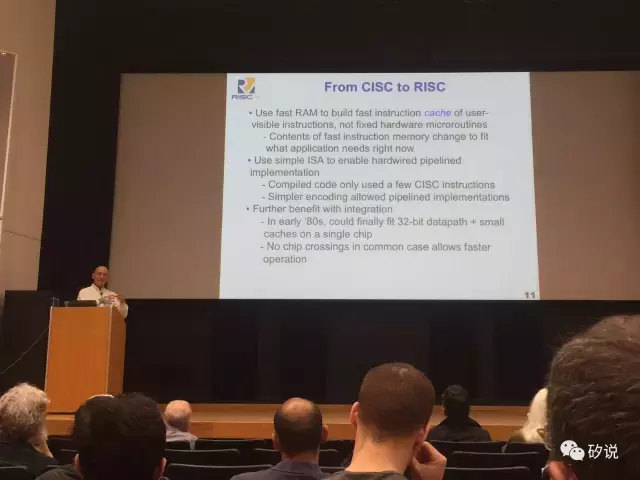

(Patterson教授在演講中)

Patterson教授的演講主題是50年來計算機體系架構(ISA為主)的回顧以及RISC-V架構。

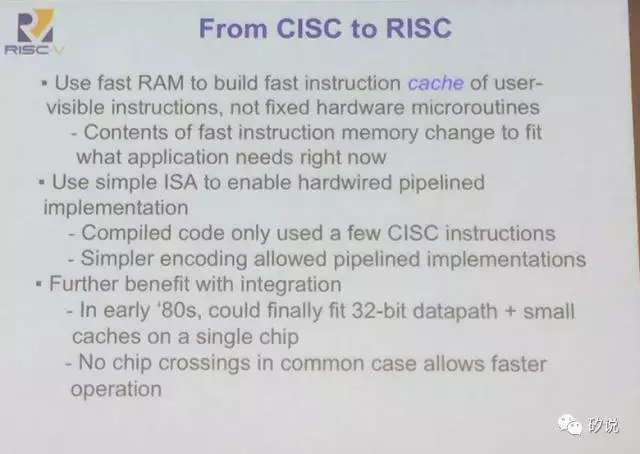

Patterson教授首先回顧了ISA的發展史。在計算機發展之初,ROM比起RAM來說更便宜而且更快,所以並不存在片上快取(cache)這個東西。在那個時候,複雜指令集(CISC)是主流的指令集架構。然而,隨著RAM技術的發展,RAM速度越來越快,成本越來越低,因此在處理器上整合指令快取成為可能。RISC的出現可謂水到渠成。研究發現計算機執行大多數程式時CISC指令集中絕大多數指令都只在極少的時間才被用到,因此專門為這些指令設計硬體並不划算。相反,使用精簡指令集(RISC)可以大大簡化硬體的設計,從而使流水線設計變得簡化,同時也讓流水線可以執行更快。

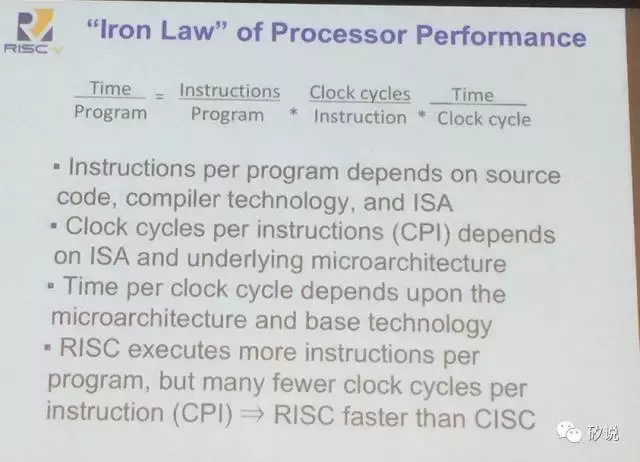

Patterson教授再次重申了評估處理器效能的指標,即程式執行時間。程式執行時間由幾個因素決定,即程式指令數,平均指令執行週期數(CPI)以及時鐘週期。程式指令數由程式程式碼,編譯器以及ISA決定,CPI由ISA以及微架構決定,時鐘週期由微架構以及半導體制造工藝決定。對於RISC,程式指令數較多,但是CPI遠好於CISC,因此RISC比CISC更快。

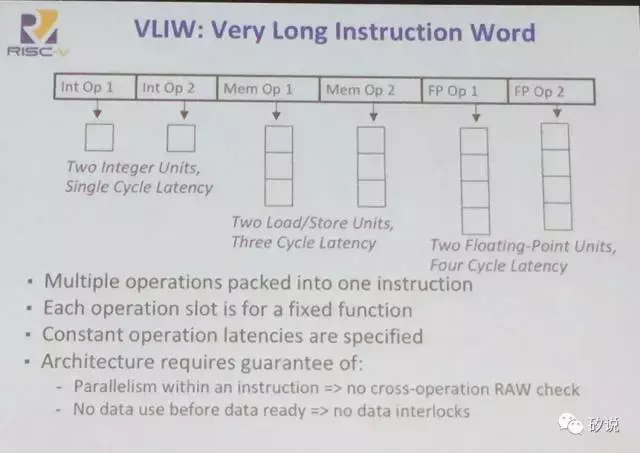

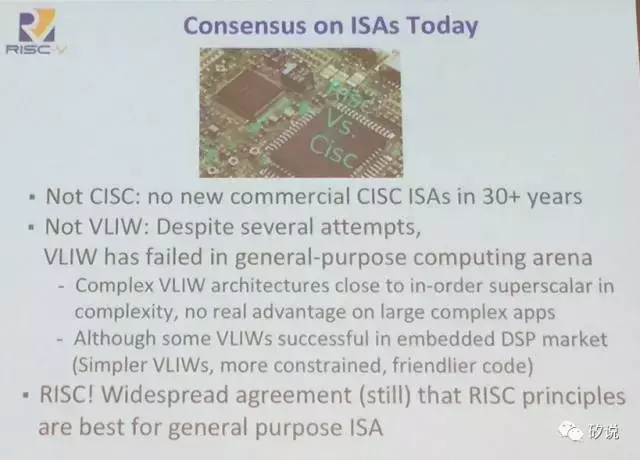

除了CISC和RISC之外,另一種流行(過)的ISA是超長指令字(VLIW)。VLIW把多個操作放在一條指令裡,因此需要一條指令中的多個操作能夠並行執行。

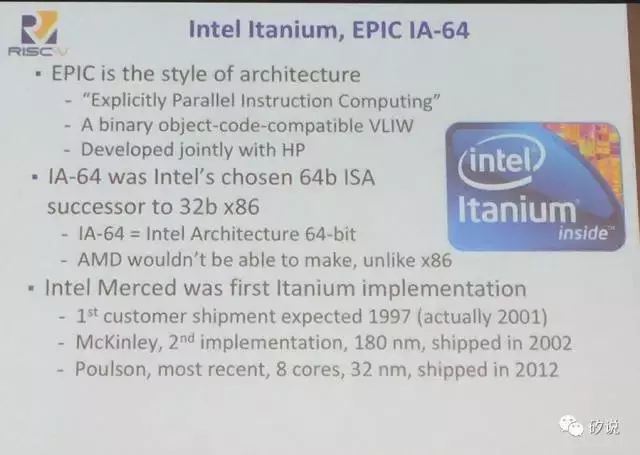

VLIW的代表是Intel Itanium(安騰),使用的架構代號是EPIC,開發的合作伙伴是惠普。安騰第一代Merced預期出貨日期是1997年,實際出貨時期為2001年;第二代McKinley使用180nm工藝,出貨時間為2002年;第三代Poulson,也是最近的一代,8核心使用32nm工藝,2012年出貨。

然而,VLIW架構遇到了巨大的失敗。VLIW的問題,包括分支預測困難,Cache miss無法解決,程式碼爆炸以及最關鍵的,編譯器過於複雜以至於無法實現。史丹佛的Donald Knuth(電腦科學領域又一位傳奇人物)表示,“安騰看上去很棒,但是編譯器根本沒法寫!”

目前處理器的ISA,已經30多年沒有新的CISC ISA出現(Intel x86表面用的是CISC但是內部有硬體把CISC轉換成RISC再真正執行)。VLIW在一些嵌入式DSP市場獲得應用,但是在其他的市場都沒有獲得成功。考慮到處理器的絕對數量,目前最主流的通用ISA還是RISC。

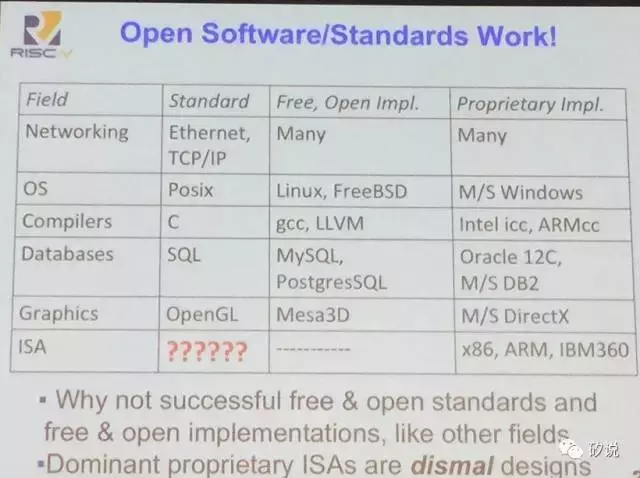

回顧完ISA的歷史,再來看看目前ISA的生態。這裡把ISA和網路,作業系統,資料庫,影像標準庫作了比較,可以看到網路,作業系統,編譯器等等領域都有主流的標準,基於該標準同時有開源免費的版本,以及商用的收費標準。然而,在ISA領域,之前並沒有公認的標準,也沒有開源免費的ISA,僅有商用的ISA,這讓整個ISA領域的生態顯得死氣沉沉。

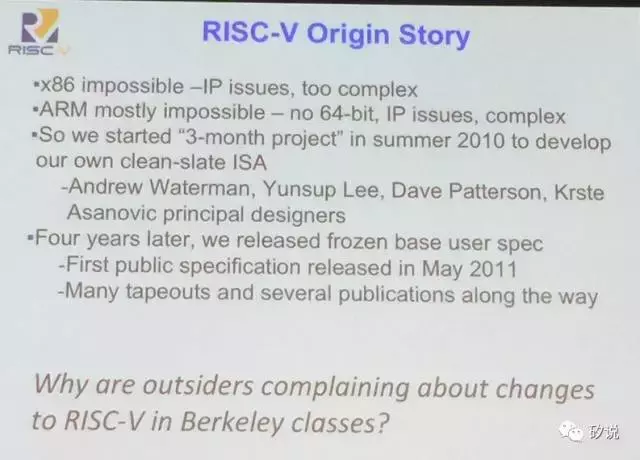

於是,RISC-V應運而生。要做開源的ISA,基於x86和ARM都幾乎不可能,因為它們都太複雜,而且還存在IP的問題。在2010年夏天,Patterson教授帶領團隊開始從頭開始設計一個乾淨的ISA。經歷了很多年,經過多次流片驗證,終於在2014年釋出了最終版spec,就是RISC-V(V是第五代的意思)。

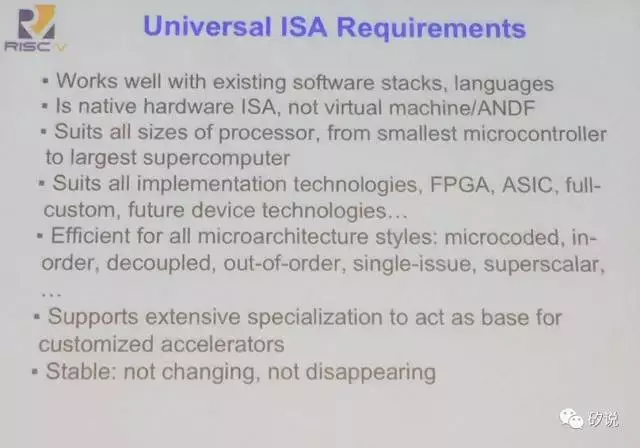

RISC-V作為一個開源ISA,首先要滿足對ISA的一般要求。首先,它必須與現存的主流程式語言和軟體相容。第二,它必須有直接硬體實現,而不是一個虛擬機器。第三,它必須有很好的彈性,能滿足小至微控制器(MCU)大到超級計算機的需求。第四,能與各種實現方式相容,包括FPGA,ASIC,全定製CPU,以及未來的其他實現。第四,需要與各種微架構配適,包括有序執行,無序執行,單發射,超標量等等。最後,還需要滿足可擴充套件性(可以作為基礎ISA,在特殊用途中加上額外的增強ISA),以及穩定性(不會一直變化,不會突然消失等等)。

除了滿足一般的需求外,RISC-V還有自己的特色。首先,它很簡單,比其他的商用ISA規模都要小很多。第二,它很乾淨,例如在使用者與特權ISA之間涇渭分明,有非常清晰的界限。另外,RISC-V中沒有與微架構或實現方式有關的特性,因此具有普適性。第三,RISC-V是模組化的ISA,它的基礎ISA集很小,但是可以根據使用者需求去載入擴充套件集。最後,RISC-V特別為了可擴充套件性和專精化做了最佳化,使用了可變長度的指令編碼,並且有許多空間以供指令集擴充套件。

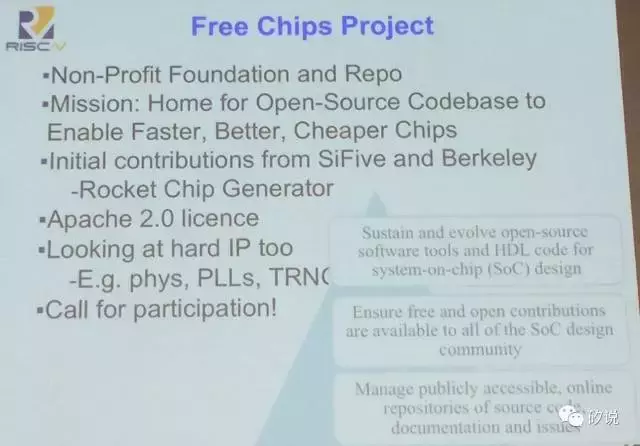

最特別的一點是,RISC-V支撐了一個開源的社群,包含了非盈利基金會以及開原始碼庫。RISC-V的願景是未來各種靈活而低價處理器晶片的基礎。RISC-V一開始的貢獻者包括伯克利和SiFive(一家初創公司),目前在徵求各類設計者加入開源社群,需要程式碼以及其他硬體IP(如PLL,PHY等等)。

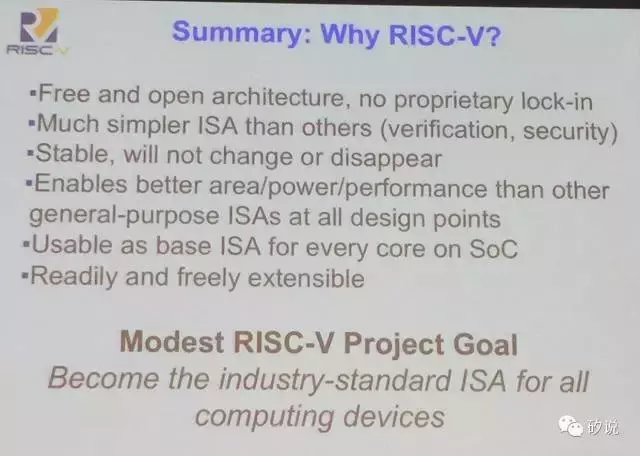

最後,總結一下幾大使用RISC-V的理由。第一,RISC-V是免費開源架構,無須付費。第二,它的ISA比起其他ISA來說簡單許多,因此驗證起來也方便許多。第三,RISC-V很穩定,不用擔心突然發生很大變化或者直接就消失。第四,RISC-V可以在各種設計中比起其他ISA更高效,面積、功耗和效能都更好。第五,RISC-V可以作為各種SoC核的基礎ISA,而且第六,RISC-V具有很好的擴充套件性,可以隨意按照需求擴充套件。現在RISC-V的小目標,是成為一種適合各種計算裝置的業界標準ISA。

John Hennessy的演講緊隨其後。Hennessy教授的演講在回顧了摩爾定律的發展之後,一針見血地指出了目前常規處理器演進遇到的瓶頸在於功耗,並且提出了目前處理器的新希望在於Domain Specific Architecture(DSA,即針對應用領域做最佳化的處理器架構,區別於通用架構)。

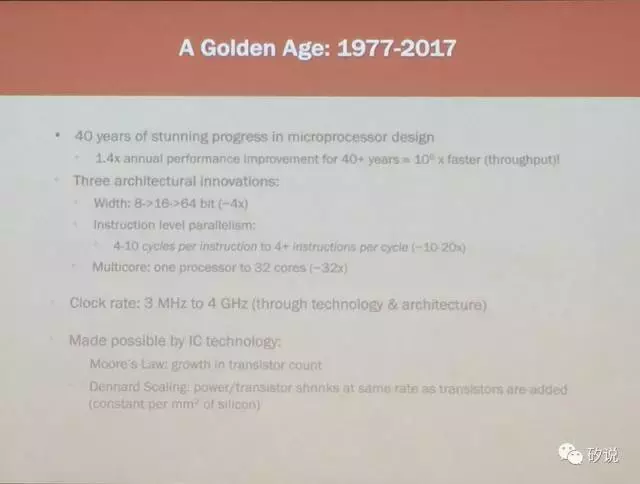

Hennessy教授首先回顧了四十年來處理器的高速發展史。四十年間,處理器效能以每年1.4倍的速度指數上升,目前效能相比於四十年前改進了約一百萬倍。在處理器架構角度,最大的進步包括位寬(由八位進化到了六十四位),指令級並行度(從最初每條指令需要4-10個時鐘週期執行到現在每週期可以同時執行超過4條指令,這是10-20倍的改善),以及多核架構(由單核演化到32核)。從效能角度,時脈頻率從3MHz進化到4GHz。這一切都是因為積體電路生產工藝進化為基礎的。摩爾定律使得處理器電晶體數持續上升,但是因為電晶體功耗和電晶體面積縮小的速度基本相同,因此在前40年間晶片單位面積的功耗基本不變。

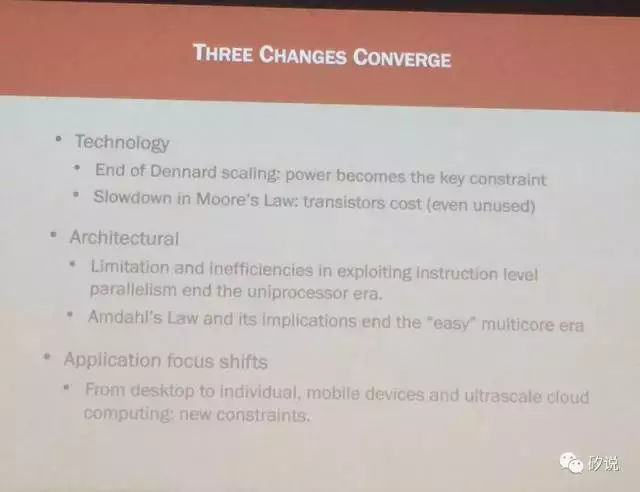

目前,三種技術趨勢讓傳統的通用處理器演進遇到了瓶頸。半導體工藝角度,Dennard Scaling規律結束,晶片功耗急劇上升,同時摩爾定律減緩,電晶體成本不降反升。從架構角度,指令級並行已經到達極限,單核時代已告結束;而Amadahl’s Law提示多核架構的速度提升取決於程式中有多少部分無法並行執行,多核架構目前的速度提升也變得越來越慢。從應用角度,處理器的應用場景從原來的桌面電腦變成了個人移動裝置和雲端超大規模伺服器,這也帶來了新的設計約束。

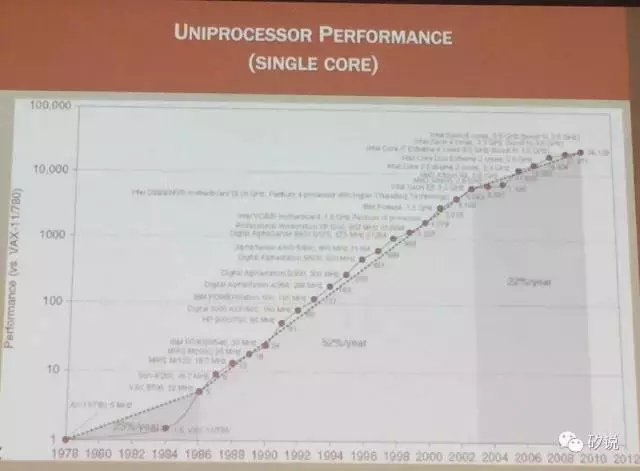

從單核處理器的速度進化趨勢也可以印證之前的觀點。從上世紀90年代到本世紀前五年,單核處理器的效能以每年50%以上的速度提升,而到了2005年後,但和處理器效能的提升速度降到了每年20%左右。

從單核處理器的速度進化趨勢也可以印證之前的觀點。從上世紀90年代到本世紀前五年,單核處理器的效能以每年50%以上的速度提升,而到了2005年後,但和處理器效能的提升速度降到了每年20%左右。

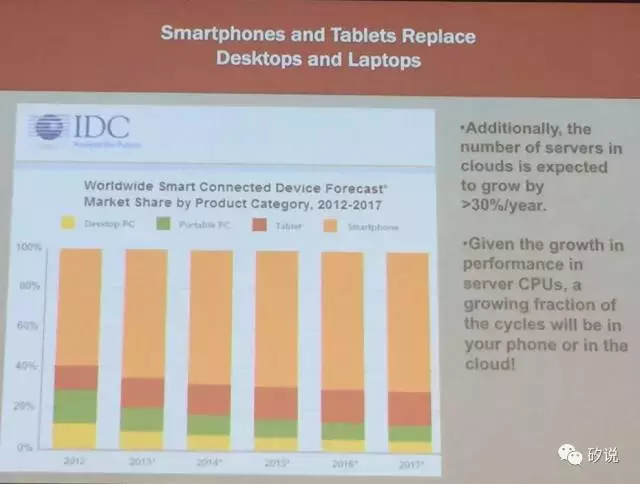

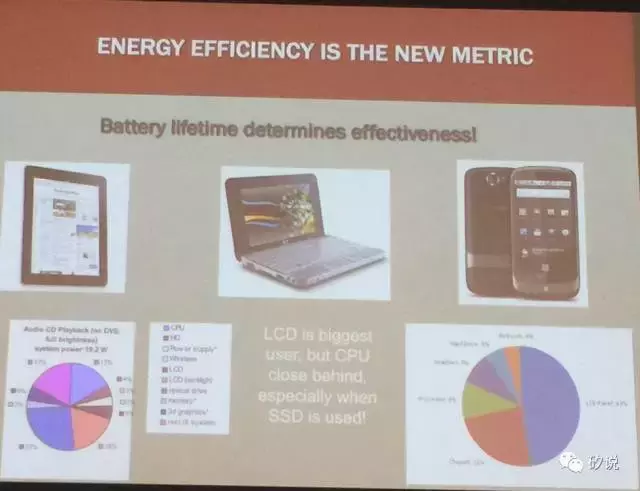

隨著市場份額的變化,處理器的設計需求也發生了變化。能效比正在成為目前最重要的指標。在移動領域,由於電池容量的限制,必須注重能效比。目前,處理器在移動裝置中已經成為繼螢幕之後能量消耗最大的元件,因此移動裝置中處理器能效比是最關鍵的問題。

在另一個未來處理器最大市場——雲端伺服器市場,能效比也是最關鍵的指標。目前資料中心的成本中,散熱已經成了最大的成本之一,為了減少成本必須考慮處理器能效比。

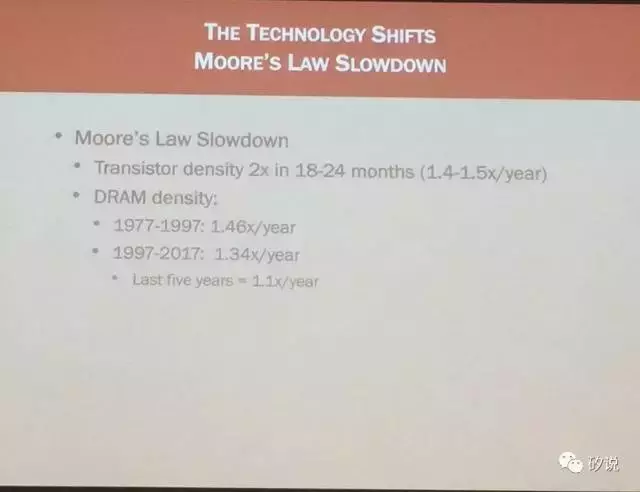

半導體工藝進化趨勢的變化也很重要。摩爾定律遇到瓶頸是近年來半導體業最深刻的變化。DRAM密度變化在1977-1997年是每年1.46倍,1997-2017年平均密度變化是每年1.34倍,而在過去五年平均密度變化是每年1.1倍。一個更令人驚訝的事實是,DDR4標準DRAM的頻寬雖然比DDR3大很多,但是DDR4記憶體的內部速度實際上比DDR3慢!這在過去半導體產業按摩爾定律蒸蒸日上的時代是難以想象的。

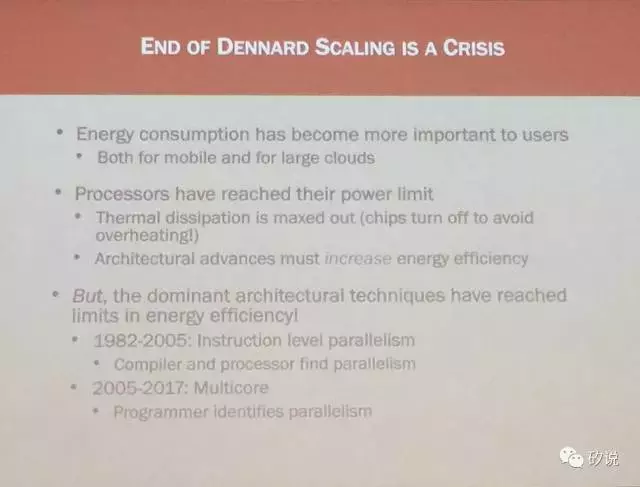

另一個關鍵的半導體工藝趨勢變化是Dennard Scaling不再有效。Dennard Scaling是早期半導體工藝變化的規律,即將電晶體尺寸和電源電壓一起變化,單位面積電晶體的總電容上升,但是電源電壓在相應變小於是總體的單位面積能量消耗基本保持不變。Dennard Scaling規律從1977年保持到了1997年,在這之後慢慢失效,例如從2007年到2017年(電晶體特徵尺寸由45nm縮小到16nm),每塊晶片的總能耗變大了3倍。

Dennard Scaling的結束對於傳統處理器設計方法來說是一個危機。能量消耗對使用者來說越來越重要(無論是對移動裝置還是雲端伺服器),而且處理器散熱已經接近了極限。處理器架構必須改善能效比,但是傳統通用架構設計方法的能效比已經到極限了。

Dennard Scaling的結束也意味著在能效比約束下,堆核數已經很難增加效能。再增加核數就會導致Dark Silicon,即晶片的許多核會很多時間處於待機狀態,從而導致很高的成本(編注:例如目前移動處理器流行的大小核架構,通常同時只會開啟高效能大核或者低功耗小核)。所有核開啟時,處理器功耗非常大,會導致散熱問題。舉例來說,目前22nm工藝製造的最大多核處理器是Intel E7-8890,有24顆核心,執行在2.2GHz,最大功耗為165W。在2021/2022年,假設可以使用11nm工藝,96核心處理器執行在4.9 GHz,那麼在165W功耗的限制下,只能開啟54個核心,功耗限制放鬆到180W可以開啟59個核,限制放鬆到200W可以開啟65個核。但是要同時開啟96個核,則功耗實在太大,很難實用。

為了提高能效比,一種很有希望的架構是針對應用領域做最佳化的專用領域處理器架構(DSA)。DSA的優點在於,可以為特定的一類應用(注意不是一種應用,而是一類)做架構最佳化從而實現更好的能效比。相對於通用(general purpose)處理器,DSA需要設計時考慮專用領域的特殊需求,也需要設計者能對該領域有深入的理解。DSA的例子包括為機器學習設計的神經網路處理器,以及為影像和虛擬現實設計的GPU。DSA設計將會成為處理器架構的新趨勢。

Q & A

Q:請問除了之前演講中提到的以外,還有哪些處理器領域的未來趨勢是值得關注的?

A(Patterson):我認為未來之星是深度學習領域的DSA處理器。深度學習的重要性我想在座的都很清楚。另外,使用更高階的設計描述語言,例如Chisel,來加速設計,也會成為趨勢。

Q:摩爾定律的終結對於整個計算機領域的人來說,意味著什麼?

A(Hennessy):The easy ride of software is over. 這意味著軟體行業的從業人員未來需要更多對硬體的理解。在之前,軟體行業可以不用太關心硬體,只要把程式功能實現,就算現在的硬體不能跑,過一陣新的更強的硬體出現了一定可以跑。現在,軟體必須認真考慮如何在硬體上高效執行的問題。會有更多domain-specific程式語言出現,例如CUDA。

Q:如何看待量子計算?

A(Hennessy):量子計算就是計算機領域的核聚變(觀眾大笑,“核聚變”的比方是指潛力無窮但是不知道哪一天真的能用上)。目前,量子計算的問題在於規模化,一方面需要製備更多的量子位,另一方面需要在質因數分解之類問題以外找到更多應用。

Q:如何看到FPGA?

A(Hennessy):FPGA是一個很好的技術。對於對成本不敏感的雲端應用,因為FPGA晶片已經規模足夠大可以裝下一些處理器,因此得到了很多關注。微軟在雲端大規模部署FPGA,顯然是在賭FPGA的可配置性在未來會有很多應用。Google則是把賭注押在了ASIC上(指TPU)。在客戶端,FPGA由於功耗過大,目前仍然很難得到大規模應用。

Q:對於學生們有沒有關於職業規劃的建議?

A(Patterson):在座的學生都很優秀,我想大家除了學習以外還要關注一些其他方面的能力,比如如何影響他人,如何寫作表達自己,如何與家人朋友一起享受生活等等。這些都非常重要。如果你一定要問我技術有關的建議,我要說的是,你在這裡(史丹佛)一定要上機器學習的課程。我感覺現在的人工智慧就像之前的微處理器和網際網路一樣,一定會深刻地改變我們的社會。